由于信号完整性(SI)、电源完整性(PI)和电磁干扰(EMI)等小问题,通常需要多次重复设计PCB,每次重复设计的平均成本接近28000美元,才能确保生成的设计满足其性能、上市时间和成本目标的强制要求。为了帮助消除复杂且难以诊断的布局违规,一些PCB设计软件工具会提供特有的电气设计规则检查(design rule checks ,简称DRC)。

采用DRC分析作为PCB设计过程的组成部分时,工程师可以确保其PCB符合各种不同的高阶电气设计规则的制约要求,DRC工具包含可定制的信号完整性(SI)、电源完整性(PI)和电磁干扰(EMI)以及安全规则检查,使设计人员能够在开始制造过程之前快速识别和纠正违规行为,通过运行DRC分析,可以去除容易出错的人工检查,降低昂贵的重复设计成本,进而加快产品上市时间,增强公司盈利能力。

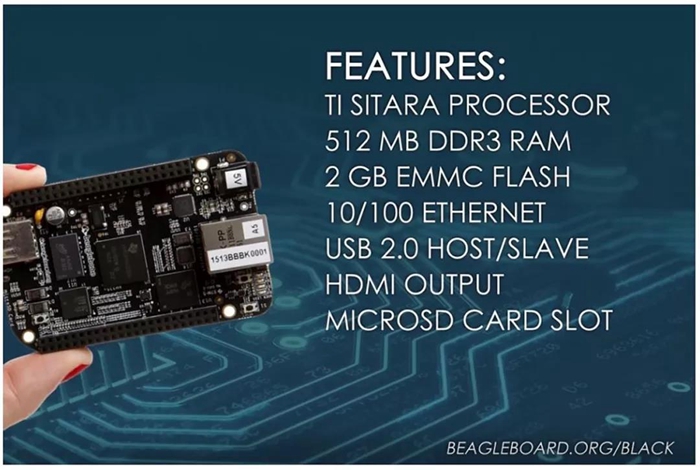

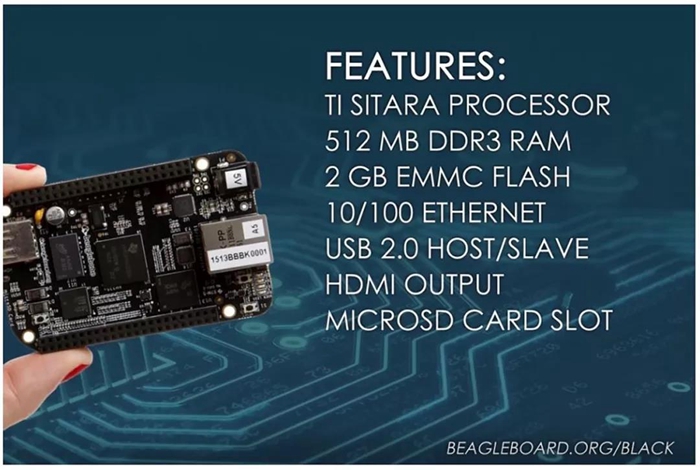

为了说明采用具备紧密集成DRC分析功能PCB设计工具的强大优势,我们将以BeagleBone Black计算机为例。BeagleBone Black是德州仪器(TI)生产的低功耗、开源单板计算机,开发人员和业余爱好者常用这种计算机,该开发板由TI Sitara处理器构成,提供性能、功耗和外设的保障,有助于降低系统成本,简化设计并扩展整体BeagleBone Black设计内的连接性。除TI Sitara处理器外,该电路板还包括512MB 的DDR3 RAM和2GB闪存以及许多物理接口和其他功能(图1)。

图1:BeagleBone Black是一个开源开发板,包含许多适用于DRC仿真的不同电气特性

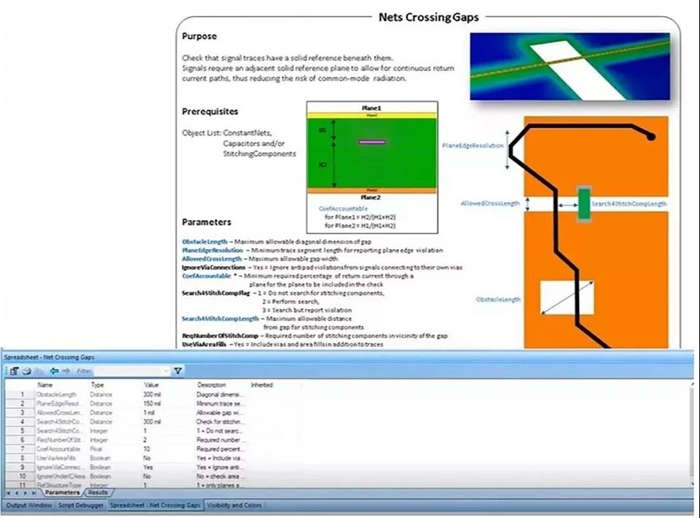

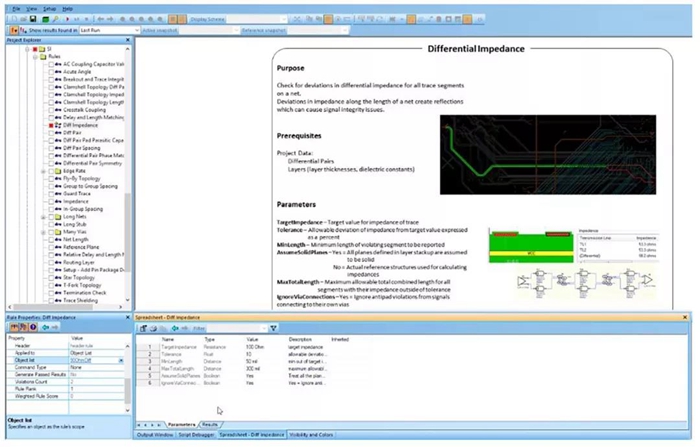

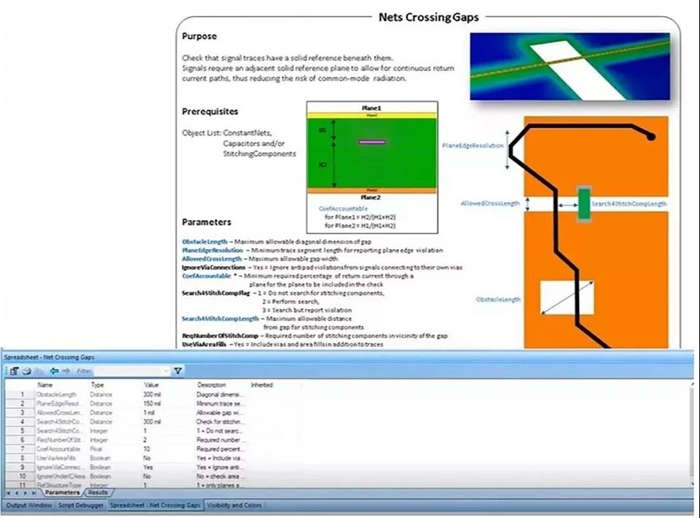

由于布局和DRC工具完全集成,因此可以直接从PCB布局窗口将PCB设计加载到DRC中,DRC中的规则具体分为SI、PI、EMI和安全性类。每个单独的规则都包含一个描述性的概述页,使设计人员可以轻松选择对其PCB布局运行最重要的测试。图2显示了DRC中网络交叉间隙规则的概述页。

图2:DRC工具中的网络交叉间隙概述页,其中包括简要说明、图形图像和描述性参数

当高速网通过分割平面时,信号走线会产生阻抗不连续,可能导致不想要的反射、辐射和串扰。随着当今PCB设计的复杂性和密度的增加,查找和审查通过分割面的网的所有实例是繁重的人工过程。此外,标准仿真工具通常不会检查,当在DRC中运行网络交叉间隙规则时,很容易精确确定可能出现的阻抗不连续。

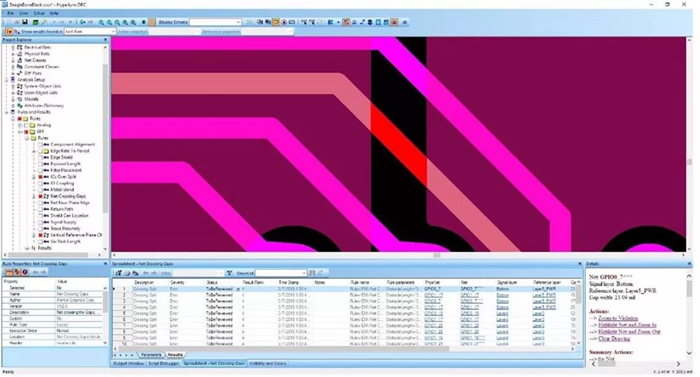

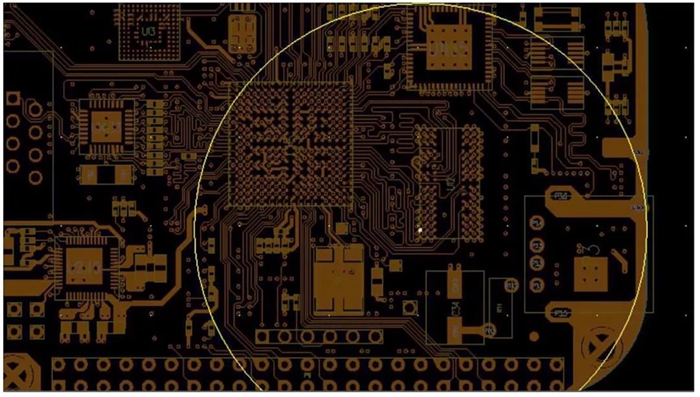

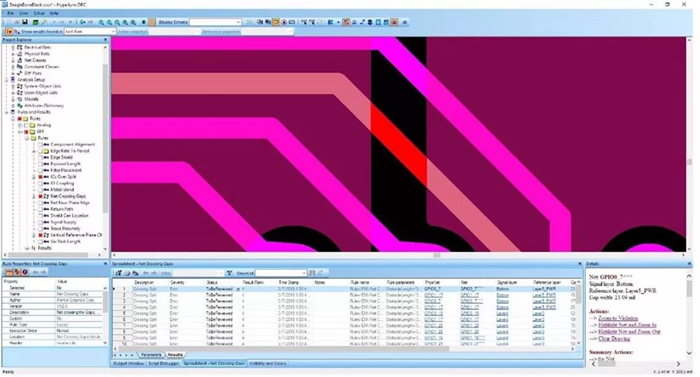

运行规则后,设计人员可以选择电子表选项以显示该测试结果。通过单击电子格选项中特定的违规事件,工具将跳转到PCB设计中该错误的确切位置(图3),会突出显示与该违规相关的任何部件或走线。

图3:当选择违规规则的实例时,DRC工具将可在窗口内缩放PCB设计中的违规位置

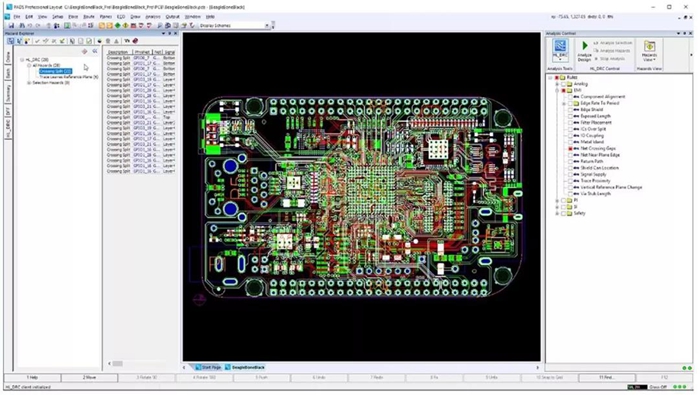

通过紧密链接的布局和DRC接口,来自DRC客户的违规数据将自动加载到PCB布局工具中,可使设计人员轻松地对其布局进行任何必要的更改,而无需在工具之间手动交叉引用,为确保在对设计进行更改后清除违规,可使用链接的DRC客户端直接在“布局”工具窗口中运行或重新运行任何选定的规则,此功能如图4所示。

图4:在PCB布局工具内部可显示集成的DRC客户端,一旦完成PCB更改,该客户端可于轻松运行或重新运行规则

BeagleBone Black设计包含许多差分对,其中两个具有90欧姆的差分阻抗,已在布局工具的约束管理器内部构建了这些90欧姆差分对,包含在单独的约束类中,由于布局和DRC之间的紧密集成,PCB工具中创建的约束类定义也将在DRC工具中自动定义,在DRC中,设计人员可以从约束类快速创建对象列表,允许他们有选择地仅在那两个90欧姆差分网上运行下一个规则。

在设计差分阻抗走线时,一对走线的长度、间距和导通孔数/位置的对称性对于适当的功能是必不可少的。差分对规则将检查这些属性是否在给定网中所有走线部分边界内是一致的,可以在图5中看到差异对规则的概述页,其中包括在属性区域中选择的用户定义对象列表。

图5:DRC中的差分阻抗规则检查差分走线上的潜在阻抗违规,通过在属性部分中选择用户定义的对象列表,可以在指定的网上有选择地运行规则

利用DRC的可定制属性,设计人员可以轻松定义规则参数,例如走线上的目标阻抗以及允许的最小和最大走线长度。由于正在测试的特定差分走线具有90欧姆的差分阻抗,因此在运行规则之前,目标阻抗参数应定义为90欧姆,DRC可以灵活地为各个设计参数定制每个规则,从而减少假违规并为设计人员提供更多控制。

工程师面临的众多挑战之一是确保他们的设计符合每个元器件的规定要求,例如,BeagleBone Black的TI Sitara处理器数据表将VDDS DDR网旁路电容的最大允许距离定义为400密耳,如果未正确放置去耦电容,DDR3接口很可能会出现故障。

人工检查每个网络上去耦电容的位置是繁琐且耗时的过程。DRC中的去耦电容放置规则将为指定网或元器件定位所有放置不当、不存在的去耦电容。利用TI Sitara数据表获得的信息,可以在去耦电容规则中指定VDDS DDR网中的400密耳放置半径。运行规则并选择违规的具体实例后,该工具将突出显示错误的发生位置,并标示指定的400密耳测试半径(图6)。

图6:DRC工具可以定位每个不正确的去耦电容放置实例,同时显示指定的测试半径

将走线从一层布线到另一层是一种常见的设计方法,用于适应当今密集的PCB布局;但是,必须注意降低共模辐射的风险。通常,当发生平面变化时,放置在网附近的缝合电容或缝合导通孔允许连续的电流返回路径,垂直参考平面变化规则可识别信号从一层转换到另一层的实例,以及这些网附近的缝合电容器或缝合导通孔的放置。

高速网的时序对于正常功能非常重要,特别是在DDR网上,如果DDR信号在适当的时序约束内没有到达目的地,则内存可能无法正常工作,导致时序问题的原因有多种,包括由于层叠、介质特性和走线布线引起的传输线传播延迟。由于延迟问题通常由PCB的独特物理属性引起,因此延迟和长度匹配规则可以自动从设计的层叠加计算必要的值,然后检查指定组中每个网上的等效延迟和/或长度。

在使用fly-by拓扑的DDR设计中,桩长度对于功能正常非常重要,通过fly-by拓扑规则的检查,确保具有fly-by拓扑的网络在适当的约束内。

串扰耦合规则将有助于识别设计中敏感网络上不希望发生串扰的区域,串扰可能导致严重的时序和功能错误,并且人工诊断PCB的方法也非常困难。

电源/接地宽度规则检查电源和接地网上的窄走线宽度,如果电源和接地走线的设计不够宽,则网上产生的电流可能不足,这可能导致许多问题,包括但不限于,供应给元器件的功率不足以及不必要的热量产生。

信号供应规则检查集成元器件的供电平面与其连接的走线参考平面之间的不连续性。这些类型的违规可能导致潜在的强辐射,从而导致EMI故障。

过滤器放置规则会在距离连接器引脚足够近的位置检查是否存在过滤器,为了保护敏感信号以及防止辐射,滤波器用于抑制连接器上可能存在的噪声,连接器上滤波器的缺失或放置不当可能导致严重的电磁干扰问题和失效。

返回路径规则确保测试信号具有足够低阻抗的返回路径,随着当今高速电路设计要求的增加以及PCB尺寸的减小,坚持正确的返回路径规则非常重要,如果走线上的返回电流无法在导体下适当流动,则可能会选择电路的其他区域的路径,从而可能导致电磁干扰问题。

通过紧密关联的PCB布局和DRC工具,设计人员可以确保其PCB不会因忽视的信号完整性(SI)、电源完整性(PI)、电磁干扰(EMI)和安全违规而失效,DRC中的可编辑参数允许用户完全控制以使每个测试适应其特定的设计要求。据此,除了更多规则之外,DRC还可以向设计人员保证,他们的PCB可以正常工作,同时减少电路板故障和重复设计。当设计满足前端的所有先进电气规则期望时,公司可加快产品上市时间,并最终提高盈利能力。

标签:

#PCB设计

#设计检查规则