你还在使用便利贴吗?这种1979年发明的简单而强大的“沟通工具”在工程和设计部门中仍然很常见。尽管现在已经有了更现代的电子通讯技术,但许多公司仍然难以找到如此易用并且灵活的替代品。

但是,通过改变工程师设计电子设备的方式,放弃通过便利贴来传递要求,改变工程师之间提出要求和约束条件的方式,可以缩短设计时间并提高产品质量。例如,现代PCB设计工具允许定义设计约束条件,包括与高速设计和EMC相关的约束条件,例如连接的拓扑结构(布线引脚顺序)或过冲和时序预算。

图1:常见的与PCB设计

随着元器件和PCB变得越来越快、越来越复杂,这些约束条件也变得越来越重要。但是很难在整个设计过程中发现并一直使用和遵守这些约束条件,并且要牢记彼此可能会相互矛盾。便利贴特别适合这项工作,它只包含设计师当前所使用的约束条件的简单草图,是一种非常简洁的方式;然而,保留这些信息并在以后使用是非常困难的。

自适应设计

使用强大的约束条件方法是一把双刃剑。尽管通过包含约束条件会使设计过程变得更加安全,但也很容易形成过度约束,使得布线和布局无法完成。即使纸质的设计指南也可能会使产品生产不经济,除非在设计过程中应用大量工程知识。这意味着设计工具必须具有自适应能力,能够针对设计中的各个阶段发生的变化做出反应。结合这些元素非常繁琐,但是这样做可以让设计师在第一遍设计中就达到最佳效果,而不用通过多次尝试。

在PCB设计中,属性(或约束条件)和规则一直都会存在,设计人员会尝试实现其设计目标,特别是在基于元器件原始属性的系统中。但属性本质上只是关于引脚、元件和线路的数据,而约束条件是必须遵守的要求。举个例子,最大延迟时间和错误标记必须标记为能正常工作或可能存在风险。这些可以简单作为设计属性中的一个功能,但是如今的约束条件通常更加复杂,并且有时彼此相关(例如,在高速存储器中,字节通道和从数据/地址信号到选通和时钟信号之间的关系)。约束条件必须存在于设计过程中的所有不同阶段,从原理图到摆放元件再到布线。

实验空间

工程师们经常会遇到的一个重大问题是实验环境(便利贴,继续我们的比喻)与设计过程是分开的。虽然这两项任务经常分开进行,但一旦条件合适,将这些在虚拟设计中开发出的约束条件转移到真实世界的设计中也至关重要。

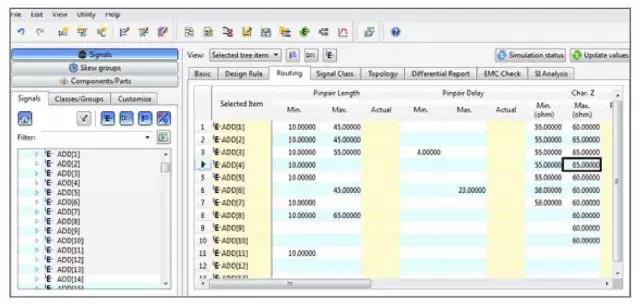

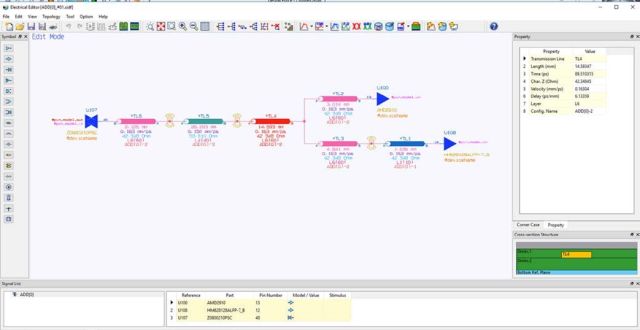

图2:约束条件浏览器Zuken CR-8000的示例

现代EDA工具使用了这种方法,并通过约束条件管理机制将设计中从原理图到制造的所有约束条件数据都保存下来。然后设计师可以浏览这些约束条件并修改它们。这种方法的主要问题是将约束条件存入数据库中,而没有输入大量数字和数据。需要重点考虑的另一个方面是约束条件不仅会影响设计的物理实现,还会影响信号质量和噪声特点。

包含约束条件设置(包括将拓扑分配给网络或网络组)的图形化拓扑编辑可轻松实现约束条件继承。真正的布线拓扑提取和便笺本编辑使得设计人员能够查看“假设”设计,就像在便利贴背面的画图一样。

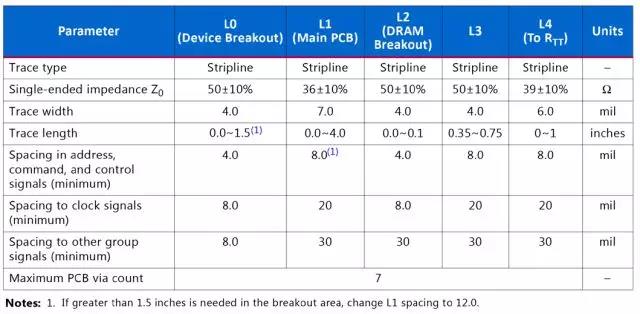

图3:JEDEC DDR4拓扑规则和等效的CR-8000拓扑模板

例如,如果内存总线以其当前速度的2倍运行,或者传输线长度减半,会发生什么事情?系统的重要组成部分是能够在设计快照(方案)中验证约束条件,并能够在开发时脱离其他实际系统设计,然后自动存入约束条件数据库。那些“假设”方案像独立的小设计一样,它们可以以相同的方式分析参数,包括信号速度、串扰和失真。从这些简单的子设计元素中得出的约束条件可以反馈到约束条件数据库中,从而完成设计的闭环。

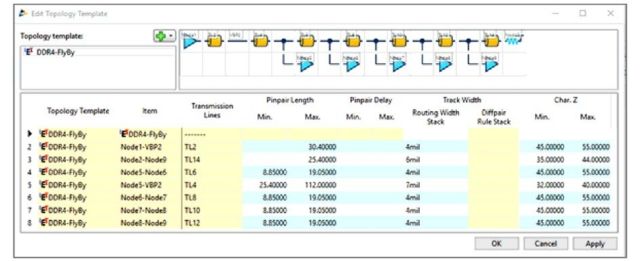

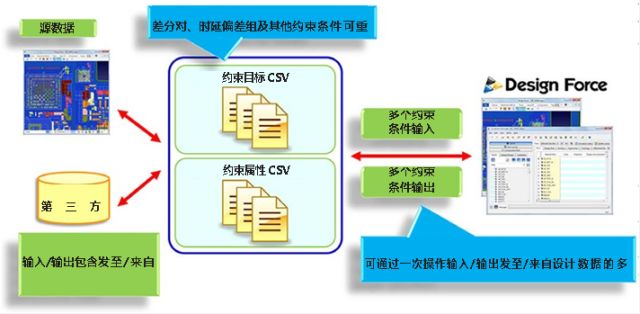

图4:导入/导出约束条件

约束条件可以传递和附加到配电网络(包括诸如电容器和电阻器之类的串联无源元件)和网络组(例如总线和网络类)非常重要,而非仅仅传递和附加到单个特定的网络。这在约束条件的使用中是一个很大的优势,这样,在大型系统中,约束条件就可以更快地执行。约束条件可以通过导入/导出到如.XML和.CSV的标准格式(图4)再次使用。

闭环设计/仿真

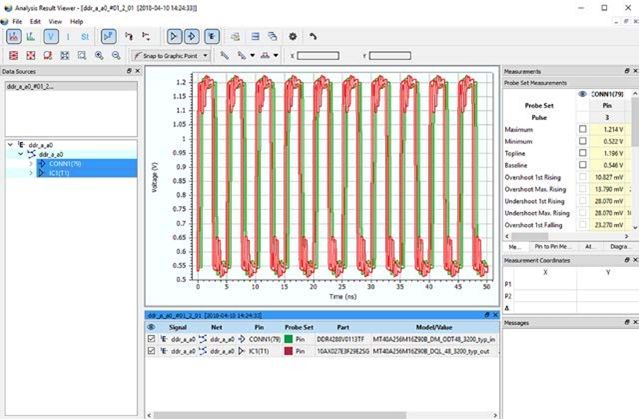

如今,除了像网络长度和间距这样的几何约束条件外,还必须满足电气要求,如专用延迟、延迟差(=误差)或失真/过冲。信号完整性仿真比使用延迟和过冲评估更准确。约束驱动设计过程的关键部分是在整个过程中都可以使用仿真来确定是否满足约束条件。这需要对工具体系结构进行根本性的改变。

传统上,SI仿真是布局后的事情,在设计完成或布线确定之后进行。有了现代约束条件驱动工具后,仿真引擎就可紧密集成在设计流程的每个操作和阶段中。SI验证可以在时域和频域中执行。时域仿真在非线性有源元器件建模时有优势;频域仿真在建模电容和电感的效果方面往往更好。

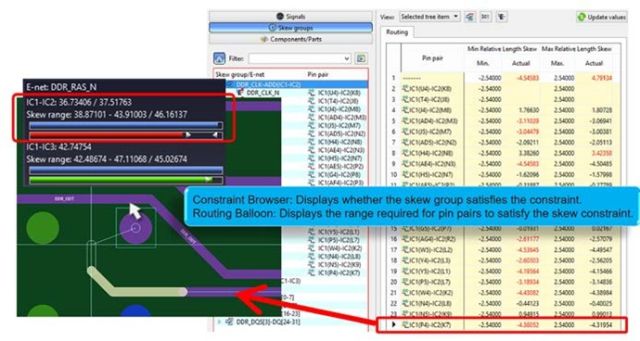

随着电路板速度的提高,电容和电感相对于非线性器件的重要性也不断提高,但使用ZukenCR-8000等工具,工程师可根据分析的重点来选择模拟区域。在布线过程中,这意味着每一条线路中的要素一旦完成布线,就可以进行仿真,再将结果反馈给布线工具。这意味着布线解决方案会收敛于约束条件内的值,而不是在布线全部完成后进行仿真时,发现某个部分超出约束条件范围,然后必须重新进行一部分或全部布线。约束条件浏览器和布线引擎之间的实时通信(图6)使工程师能够高效地优化布线结果。

图5:网络拓扑的信号完整性仿真

图6:约束条件管理和布局之间的通信

约束EMC / EMI

接下来,我们来讨论需要在设计中考虑的电磁兼容性(EMC / EMI)约束条件,它采用了与信号完整性、热管理和制造类似的集成方式,但是又有所不同。由于EMI与设计的物理布局密切相关,所以只有在设计进入物理阶段后才能进行分析。为了能够进行高效设计验证,我们与密苏里大学罗拉分校(现为密苏里科技大学)合作开发的算法已经应用到了EMI的最坏情况快速预测检查器中(图7)。

图7:嵌入式PCB的快速EMI验证

这使得我们能够在给定频率下对差模和共模噪声(如寄生天线和I / O耦合)进行EMI分析、电源层辐射分析,包括解耦分析。这种方法更适合并行PCB设计过程,而不是传统的全波数值电磁分析方法。

但是,过度约束还是有可能发生,导致设计不可行或不经济。层数、制造电路板所需的制造技术以及组装参数等方面的工程权衡非常复杂,必须由设计人员与生产团队共同确定。达成共识后,EDA系统需要足够灵活,才能将这些参数纳入构成设计数据库一部分的技术文件中。

你可能会觉得弄了这么多东西就为了替代便利贴是不是有点太麻烦,但是这样才能解决过去几年中一直在阻碍约束驱动设计的问题。如今,诸如CR-8000的工具能够为工程师提供一种实用的约束驱动设计方法。在过去,通常需要来自多厂商系统混合搭配的工具,现在可以通过一个单一、一致的现代化设计工具实现,这些工具使得我们能够对2D和3D单板和多板系统进行约束驱动设计。

Ralf Bruening,Zuken EMCTechnology Centre 产品经理和高级顾问,主要负责Zuken的高速设计、SI和EMI验证工具。