很荣幸地告诉您,这是我的第100篇“超越设计”专栏文章。I-Connect007是一个非常棒的合作伙伴,我总是迫不急待地期盼每期杂志的发布,他们对于我的专栏文章的编辑、排版和制作总是富有新的创意。

I-Connect007成立于1999年,现在是业界运营时间最长的电子媒体门户网站。个人职业的发展和持续学习是如此重要——特别是在一个相对新且不断变化的行业中,设计师需要不断努力。I-Connect007凭借其3个在线杂志——Design 007(包括Flex007)、PCB007和SMT007,为行业提供业内专家共享的最新资讯。

我的第一篇“超越设计”专栏于2011年在线发表。多年来我只在一次度假时延误了1篇专栏文章的发布。所以我得努力克服懒惰的毛病!当我第一次撰写一个定期专栏时,我可能只是想将SMT的高级设计课程内容——自1994年以来我一直在澳大利亚和新西兰开办的课程,分成若干部分进行介绍,但是我从未想过竟然达到了100篇。

“超越设计”专栏专注于高速PCB设计、信号完整性和电源完整性以及EMC设计方法,为了在第100篇专栏文章进行总结,我回顾了过去的99篇专栏文章,并总结了我认为对高速PCB设计人员最具启发性的关键点,下面按照逆序逐一简要介绍。

10. 最小回流阻抗

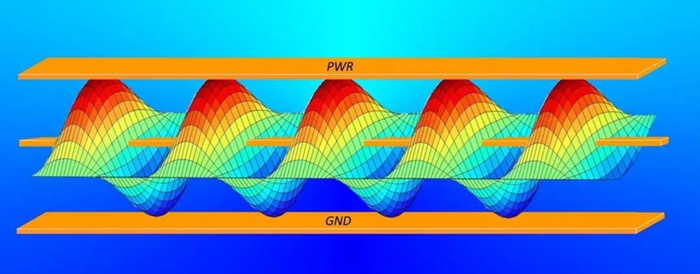

多层PCB中的接地层允许设计人员使走线在任何地方接地,无需布多条走线,需要接地的网可直接布线到另一层的接地层。但是这是一种简单的方法。还应该考虑电源分布网络(PDN)的存在和相互作用,以及返回电流的流回方式和位置。逻辑示意图掩盖了对无意识信号路径的运行至关重要的细节,而这些信息对于理解信号性能、串扰和电磁辐射至关重要。

计划叠层时,要知道哪些平面(电源层或接地层)将是关键信号的返回路径,并确保有无阻碍的返回路径。这一点的最佳解决方法是设想在参考平面上布置与每个信号走线相邻的返回走线。电流将流向哪里,是否畅通无阻?与每个信号层相邻的参考平面允许返回电流的流动尽可能接近信号走线,以减小感抗和环路面积。

9. PDN(电源分布网络)和电容选择,第1部分和第2部分

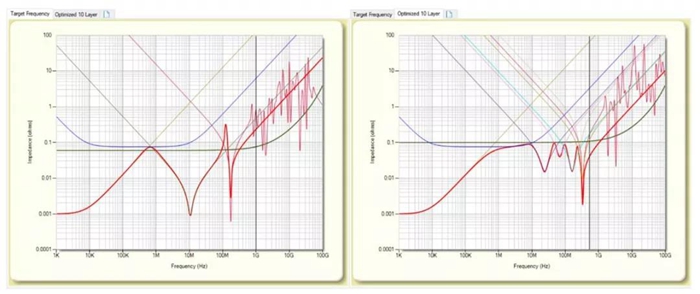

这篇由两部分组成的专栏文章重点介绍了电容的选择和3种分析PDN的替代方法:

1. 目标频率

2. 每十倍频对应一个电容值

3. 优化电容值

传统上一直使用目标频率方法。该方法以精密的频率为目标,用于降低交流阻抗以及特定频带内的EMI,使用每十倍频对应一个电容值或许多优化电容的替代方案,实现在宽频带上稳定所需阻抗的AC阻抗。

8. 信号完整性,第1至第3部分

随着系统性能的增加,PCB设计人员面临的挑战变得更加复杂。更低的核心电压(lower core voltages)、高频率和更快的边沿速率的影响迫使我们进入高速数字领域。但实际上,这些问题可以通过经验和良好的设计方法来克服,如果目前没有经验,可以阅读一下这篇由三部分组成的信号完整性文章,包括以下内容:

·先进的IC制造方法如何对信号质量和辐射发射造成严重破坏

·串扰、时钟和偏移对信号完整性的影响

·大多数设计师在信号完整性方面容易出现的问题,以及如何避免常见问题

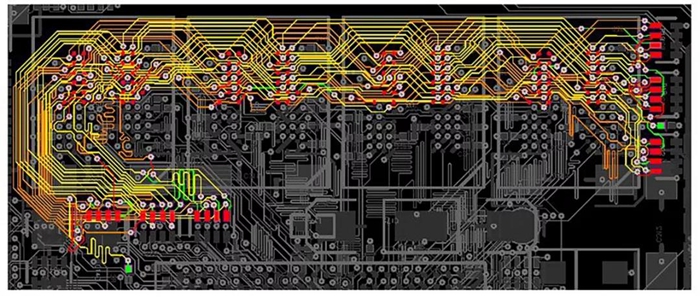

7. 电源层和接地层,第1部分和第2部分

高速数字PDN必须在PCB上需要通信的所有IC之间提供低感阬、低阻抗路径。为了降低感抗,必须最小化电流所包围的环路面积,实现这一目标的最实用方法是在多层叠层中使用电源层和接地层。在这篇由两部分组成的文章中,我阐述了层的替代方案,为什么层可用于高速设计以及适合具体应用的最佳组合。

6. DDR3 / 4 Fly-by拓扑:匹配和布线

DDR3 / 4 fly-by拓扑类似于菊花链或多点拓扑,但链中的每个存储器件具有非常短的桩线以减少反射,fly-by拓扑的优势在于它可支持更高频率的运行,可改善大负载信号的信号完整性和时序。如果采用的是高频DDR4,那么通道的带宽需要尽可能高。而且,由于目前极快的边沿速率、桩线的排序和终端匹配及相关负载,使信号质量产生明显的差异。在本专栏文章中,我探讨了如何更好地实现DDR3 / 4 fly-by拓扑的布线。

有关更多背景阅读,可查看我的《DDR、DDR2和DDR3的PCB设计方法》系列文章,该文分为两部分。

5. 微带共面波导

典型的共面波导(coplanar waveguide ,简称CPW)由一对接地平面铺铜分开的微带导体带形成,所有这些都固定到介质的同一层上。在理想情况下,介质的厚度是没有限制的,但实际上,如果它足够厚,电磁场在离开电路基板之前就会消失。当在介质的相对侧上提供接地参考平面时,就可形成共面波导的变体,被称为导体支持或接地的共面波导(CPW)。共面波导(CPW)已经在射频和微波设计中使用多年,因为与传统微带相比,它们可在极高频率下减少辐射损耗。随着边沿速率持续上升,它们又开始流行。在本专栏文章中,我描述了共形场论如何用于模拟微带共面波导的电磁效应。

4. 信号的返回路径

所有PCB设计人员都应该知道串扰对信号完整性的影响。当信号走线接近干扰信号时,该信号的一部分会作为噪声电磁耦合到受干扰的走线中。我之前提到过,电流必须返回到起点形成闭合的回路。那么,当电流在铜走线上回流时,参考平面的返回路径中的串扰怎么样呢?本专栏文章紧接我之前的专栏“返回路径不连续”,并详细阐述了信号中“返回路径”的串扰。

3. 下一代PCB:基片集成波导

(Substrate-integrated Waveguides)

随着PCB传输频率达到100 GHz甚至更高,目前的主流PCB技术(铜互连)正在达到其性能阈值,最终介质损耗、铜粗糙度和数据传输容量是主要原因。但是,PCB互连的最大性能限制是导体的尺寸,与传统的传输线相比,金属波导是更好的选择,但它们体积庞大,昂贵,且本质上是非平面的。

最近,基片集成波导(SIW)结构已成为可行的替代方案,并且适用于电磁波的高速传输。SIW是平面结构,由两排周期性的PTH导通孔或槽连接介质基片的顶部和底部的铜接地平面。在本专栏文章中,我总结了基片集成波导及其与微带传输线的结合。

2. 叠层计划,第1至第5部分

设计方法会随时间而发展变化,特别是模拟电磁场和返回电流路径的设计方法。在关于叠层计划的前4篇专栏文章中,我介绍了使用信号层和电源/接地层组合的传统叠层结构。但是为了达到叠层设计的更高设计水平,不仅需要考虑叠层中信号和平面层的布置,还需要构思通过电路基板传播信号的电磁场。第5部分介绍了叠层结构设计中的所有最新概念。

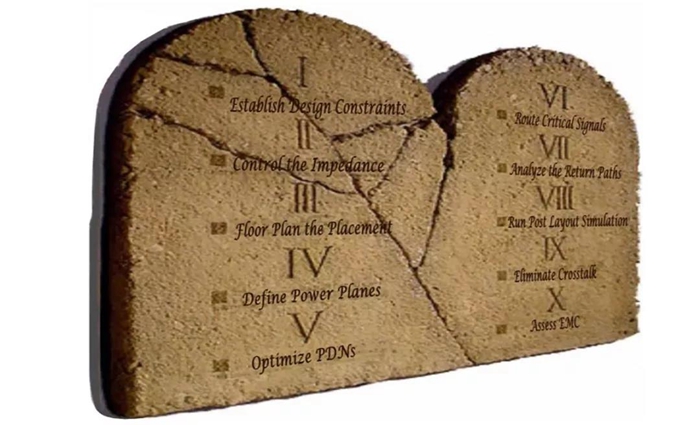

1. 高速PCB设计的10条基本规则,第1至第5部分

多年来,在众多已发表的技术文章中,我专注于高速设计、信号完整性和电源完整性以及EMC设计方法,所有这些都有需要考虑的关键点并提供了大量的宝贵信息。在这个由5部分组成的系列文章中,我列出了为实现成功的高速PCB设计、可靠地满足预期要求需要考虑的10个最重要因素。这10条黄金法则应该成为所有高速PCB设计师的首要检查表。

1.建立设计约束

2.控制阻抗

3. 平面计划安排

4. 定义电源层

5.优化PDN

6. 关键信号的布线

7.分析返回路径

8. 运行布局后仿真

9.消除串扰

10.评估EMC

展望未来,你对我第101次专栏的主题有没有什么好的建议?“信号完整性101”怎么样?欢迎通过我的专栏作者页上的链接提出建议主题。

参考文献与文中给出的10大主要关键点编号标题相对应,建议按照整个专栏中相对应的标题进一步阅读,点击即可查看更多相关内容。