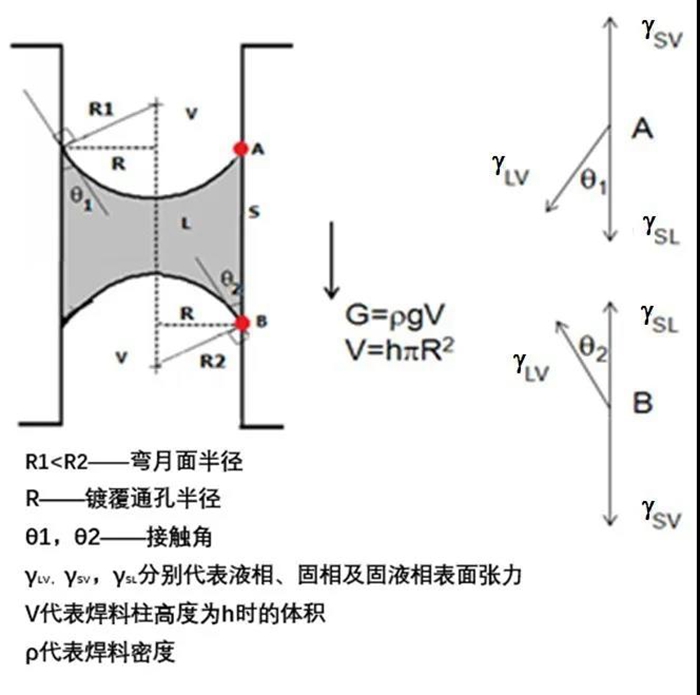

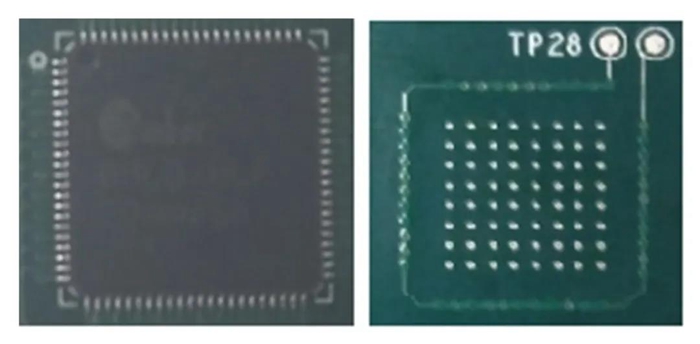

行业中用于减少空洞的策略取得了不同程度的成功,其中包括管理回流焊曲线参数、焊膏沉积量和焊膏类型、模板上不同形状的开孔切割、有或无阻焊层网的散热焊盘形状、真空辅助的回流焊、PCB载板扫描、使用预成形焊片、在贴装元器件和回流焊操作之前给元件焊盘上锡、在焊点脚趾处套印的I/O开孔设计、以及暴露的焊盘内导通孔[1–8]。这些方法的变异以及组合使用对底部端子元器件(BTC)散热焊盘上空洞的控制都在批量生产中起到了不同程度的作用 。 本文讨论的方法会涉及暴露的焊盘内导通孔的使用。实验过程中为两种QFN元器件设计了专用测试载体。主要的变量是元器件尺寸、散热焊盘上暴露的导通孔数量、导通孔间距、导通孔大小和焊膏覆盖面积。本实验主要研究散热焊盘空洞量和焊料沿孔壁芯吸至PCB另一侧并凸起。 实验结果表明,不论导通孔直径和焊膏覆盖面积是多少,焊料都会沿着暴露的焊盘内导通孔向下芯吸。除了这个研究结果以外,并未发现诸如元器件倾斜、偏移、断路或桥接等缺陷。特定配置能够让散热焊盘中形成的空洞率保持在25%以下;但其他配置会让散热焊盘中形成的空洞率高达50%。本文还会讨论电路板厚度及导通孔阵列的几何结构对散热焊盘焊料覆盖面积和空洞量的影响。 简介 根据假设,当暴露的导通孔/镀覆孔(PTH)的直径足够小(电镀前钻孔直径≤10 mil)时,可以防止熔融焊料芯吸至导通孔内,同时又能让回流焊操作过程中产生的挥发物逃逸,从而最大程度地减少BTC散热焊盘上形成的空洞。接下来的问题是,如果有意将焊料印刷在这些暴露的焊盘内导通孔上,空洞大小是否会变化,如何与焊膏沉积在暴露的导通孔之间时发生的情况相比较。 从这个假设入手,图1简要概括了作用在暴露的焊盘内导通孔内有限量焊料上的力的平衡;焊料柱的高度实际上是接触角度和成品导通孔体积的函数。图1假设PTH内有可润湿表面。 图1:作用在暴露导通孔内有限体积的焊料上的各种力的平衡 平衡状态下,焊料柱的高度(h)可由等式1表示: 从焊接应用的角度来看,等式1并没有实际应用意义;当焊料接触到TH暴露的导通孔时,焊料会根据润湿能力、可得到的焊料量和加热/冷却条件芯吸至导通孔内。但有趣的是可采用等式1思考什么条件可以最大程度地减小焊料柱高度或使其为零: • 如果焊料没有润湿导通孔(导通孔未被电镀) • 如果Ѳ1 = Ѳ2 (无重力) • 如果Ѳ1 = Ѳ2 = 90°(无法成为自然方案) 因为暴露的电镀导通孔无法满足这3个条件,再加上焊料柱的假定高度和暴露的电镀导通孔半径R之间的关系,对于任何尺寸的导通孔而言,不论加工后的导通孔实际直径是多少,似乎都无法防止焊料芯吸至可润湿的电镀导通孔内。除去这种粗略计算方法以外,还要求一种切实可行的验证方法来完整地验证这一假设。为此,在研究过程中设计出了一种测试载体并在下面内容中给出了计算得出的参数。 实验结果 测试载体 本文使用的实验方法是设计出一个具有不同电镀导通孔直径和导通孔阵列的测试电路板,再设计出既可以在导通孔上印刷也可以在导通孔间印刷焊膏的模板,生产出不同厚度的电路板,组装后统计焊料的导通孔数量、空洞百分比、以及有焊料凸起的导通孔数量。 如果证明这个假设成立,那么散热焊盘中的空洞形成就会最小化、热传导也会得到优化,而且元器件的焊接点高度会均匀一致。否则,导致焊料芯吸至暴露的导通孔内的因素会是: • 印刷焊料的体积和位置 • 加工后导通孔的可焊性 • 焊料润湿能力 • 出现阻挡层(阻焊层网) • 温度值和温度梯度 • 焊料的易得性(表面张力迫使TH导通孔、电路板表面和元器件表面保持平衡状态) 图2:A-MLF88-10 mm-0.4mm -Sn 电路板的俯视图和底视图 电路板外形: • 尺寸是224 mm x 170 mm,4层结构,ImAg表面涂层 • 散热焊盘内的PTH导通孔与所有层全部相连 • 3种不同的电路板厚度:93 mil(2.36 mm)、110 mil(2.8 mm)和130 mil(3.3 mm) • 一种是间距为0.4mm的QFN元件,另一种是间距为0.5mm的QFN元件 • 散热焊盘内暴露的导通孔的阵列为2×2、5×5和8×8。 • 2种阻焊层设计(导通孔周围有或无阻焊层环) 导通孔直径按照ɸ1<ɸ2<ɸ3选择,表示钻孔的外直径(OD): • ɸ1 = 0.2 mm (~0.00787”) • ɸ2 = 0.23 mm (~0.00905”) • ɸ3 = 0.25 mm (~0.0098”) 图3:测试电路板 尽管电路板上装有2类元器件,但本文仅讨论10 mm x 10 mm、间距为0.4 mm的QFN元件。图2所示为有88个引脚、芯片尺寸为177.1 mil×177.1 mil、散热焊盘面积为8.3mm x 8.3 mm的元器件(A-MLF88-10 mm-0.4 mm-Sn)。图3所示是最终加工好的测试电路板概念图。 图3突出显示了导通孔周围出现阻焊层环的位置,并在所有参考代号上的第3行、第4行、第7行和第8行中用红色突出显示。测试电路板是对称的,每组特征都在每块电路板上重复4次。 模板设计 针对2个模板进行了计算,焊膏覆盖面积最小达到50%。使用的模板是厚度为4 mil的NiCut 。根据IPC-7093计算焊膏的覆盖面积,也就是可焊表面积不包括开口的、填充的和阻焊层侵入的导通孔在内。2个模板焊膏覆盖面积的计算及测量值如表1所示。A模板用于印刷焊膏点阵(在导通孔之间),模板B用于点涂焊膏分区(在导通孔上);图4就是其中一个示例。 对于模板B中8 x 8的导通孔阵列,计算及测量得到的一些焊膏覆盖面积值显示是100%以上;这种情况下可焊表面面积(因为出现了更多带有阻焊层环的暴露导通孔)会比总印刷面积小一些。 图4:点开孔和分区开孔示例 …… 作者团队: Alfredo Garcia, Domingo Vazquez, Ricardo Macias, Rodrigo Ibarra, Joe Smetana, Mulugeta Abtew, and Iulia Muntele 公司:Sanmina and Nokia