本次专家访谈的重点是IEEE异构集成发展路线图(HIR)。HIR是一份为 IC设计师、PCB设计师和封装设计师提供指南的文件,按照行业领域和产品性能要求划分具体章节 。Synopsys公司的Rita Horner从IC领域角度分享了她对HIR的见解,并介绍了在未来几年内HIR将如何影响PCB设计和制造领域。

Nolan Johnson:Rita,可以先做一下自我介绍,然后再来聊一聊HIR对于PCB技术人员的意义吗?

Rita Horner:我获得了电气工程的硕士学位,在电路设计领域约有10年的从业经验,主要进行晶体管级别和混合信号设计。我一开始在惠普工作,然后到其子公司Agilent工作;后又回到惠普,但我所在的公司很快又更名为Avago。我也曾在2家初创公司工作过,从事混合信号设计的相关工作。我曾经在惠普的集成电路业务部工作,其间设计过ASIC和IP,供惠普内部不同部门使用。

然后我又调到了市场营销部。8年前我加入Synopsys公司,主要从事高速接口方面的业务,直到6个月前,我调到了Synopsys的设计团队,专门研发3D IC Compiler产品。

Johnson:你的丰富工作经历非常适合解读异构集成技术目前的发展概况。你认为异构集成有哪些发展趋势?

Horner:从技术和经济角度看,3D IC是一项热门技术。半导体市场已经到了转折点——对于单个封装部件中的单个芯片,较小的技术结点无法满足所要求的集成水平。单个芯片就会变得非常大,导致无法生产。

如果了解步进光刻机的尺寸,就知道实际能加工裸晶片的最大步进光刻机尺寸受刻线限制,约为800平方毫米。如果裸晶片的尺寸过大,良率就会呈指数下降,导致部件成本非常高。更糟糕的是,像AI加速器以及数据中心和高端网络市场的高性能运算需求,都要求高性能,使一切距离变得更近,但步进光刻机的最大划分尺寸不足以满足这种高级集成需求。而对于这种高端产品,将多个部件以分别封装的形式组合在一起的方案并不可行。

Johnson:这样就很矛盾了,需要在芯片上布置实现所有功能,可是实现这么多功能又非常困难。

Horner:没错,高端运算技术需要降低延迟。这一点至关重要,因为每次从封装好的部件跳到下一个器件获取数据时,都会增加延迟。大量这类AI应用需要频繁访问存储器。如果总是跳来跳去,周转过程就会产生大量延迟,这样就很糟糕,因为处理数据的速度会很慢。把存储器放置得近一些是十分合理的。所以AMD开始做出了大动作,将DRAM存储器放得更近一些。最终,JEDEC几年前启用了高带宽存储器(high bandwidth memory,简称 HBM)标准。

就出现了一层一层堆叠的DRAM,形成可以连接到处理单元的存储区。可以是CPU、GPU或任何需要高级存取访问和低延迟的SoC。将这些器件放置得近一些,特别是在同一个封装内,你就再也不需要到封装之外经过PCB走线, 到其他封装访问获取数据,这样就能最大程度地减轻延迟并节省功率。

就成本方面来看,复杂设计的封装内混有多个芯片,含有需要考虑的多层复杂结构。如果能在封装空间规划过程中和SoC或封装设计师沟通,或者与负责将部件组装到电路板上的专人联系,这样就能进一步同时优化设计的每个部件,即可实现并行优化。封装有很多载板层,和PCB板层的概念类似,板层数量增加就意味着成本的提高。如果知道把凸缘连接放在封装载板的哪个最佳位置点能最大程度减少载板板层数量,或者知道将微型凸缘放置在哪儿可以形成芯片间的最佳连接、最大程度地缩小中介层的尺寸,就可以节省整体成本。所以封装设计师、PCB设计师和芯片设计师之间应该加强沟通,共同开发高性价比的最优方案。

Dan Feinberg:5G技术也会进一步加速实现这个目标。关于你讨论的这一问题,其中一个方式就是在制造CPU时采用chiplet。是吗?

Horner:在许多应用中,不仅因为裸晶片的尺寸变得越来越大,还因为同时要处理多项任务。有时,部件内会有40多个核芯需要并行处理。在AMD的一些设计中,有4个核的芯片,每个核内还有4个核。也就是说一个封装内有4×4共16个核。若一个大的裸晶片为了聚合多个核被分割为较小的部件,那就要确定如何分割芯片以及使用哪些接口。

Feinberg:几个月前我刚用AMD的新款芯片做了一个部件,是24线程的。用户使用chiplet时遇到的难题是温度控制。不得不使用液体降温方式,但这都不在选择范围内。

Horner:多芯片封装集成存在很多挑战。在封装中集成多芯片并不是新技术,这种技术已经存在几十年了。过去,很少有器件需要集成,之间的连接也非常少,与如今封装产品中的多芯片系统相比,这些都是小设计。随着封装中的器件越来越多,方案的良率再乘以每种器件的良率,总体良率会进一步下降。一个封装中单个芯片的良率可能是99%,假如要在封装中添加一个80%良率的器件,良率就会进一步下降为80%乘以99%。添加更多部件只会使良率下降。

不同应用有不同需求,所以才会有诸多不同类型的接口。有些I/O需要用几千条线才能形成一个链路连接。用HBM接口连接到HBM存储器堆叠,一个存储器堆叠上就要形成1000多个晶片间连接。此外,还需要屏蔽这些信号,就变得更复杂了。

Feinberg:AMD是这个领域的领导者。我一直都是Intel的粉丝,但AMD似乎开始占据了领先地位。他们似乎对7纳米的几何结构很有把握,而Intel仍在应付10纳米以上的结构。

Horner:AMD已经不再有自己的内部制造厂了,全都依赖晶圆代工厂和封装合作工厂。

Johnson:你目前在Synopsys负责的项目是在封装EDA产品中集成多个芯片。多芯片产品与HIR为行业指引的方向之间有何差异?

Horner:正如Nolan所说的,HIR涵盖很多领域,它并不仅限于一个市场或应用。很难概括。我谈过技术极限,但经济方面的因素也要考虑。如今采用先进技术结点的芯片既复杂又大,比如5纳米或更小的技术,所以即使是封装中一整块芯片的成本都很高。当达不到目标良率时,成本高得令人难以承受。封装内的异构集成可以大幅降低通往高端市场的门槛,不需要采用成本最高的技术结点设计一切就能实现高水平的集成。

Johnson:一小部分设计需要高密度结构并不意味着整个设计都要这样。

Horner:对于所需的高性能I/O,5纳米技术也许并不是最佳技术。技术结点越小,氧化物涂层越薄,阈值电压会越低,设计高速I/O就越有挑战。高速SerDes采用传统技术结点可能会更有优势,而其余运算可能采用更小技术结点更适合,可实现更高的密度。

通过异构集成可实现更灵活优化,通过混和匹配那些采用不同技术的器件,或许也可以允许器件采用更优化的工艺结点技术,而不必都封装在同一块芯片内。为了达到更小的尺寸外形,即使是过滤器件也能集成在同一封装内。这种封装实质上就是微型PCB。

Johnson:与传统多芯片模块相比,这是不是HIR与之不同的地方?似乎对技术互连方面的需求更大了。

Horner:HIR涵盖了多个市场空间,包括5G、运算技术和高性能,而且确定了这些技术,例如汽车、航空等不同市场的需求。PCB走线的线宽和线距曾经是100微米,现在在不断缩小,今天的多层PCB线宽和线距约为8微米。

Happy Holden:我曾工作过的顶尖亚洲公司都在使用8微米技术,而且是产量。他们会在一块18英寸×24英寸的面板上放置6千万到1亿个50毫米×50毫米的中介层。这是一项非常先进的印制电路技术。

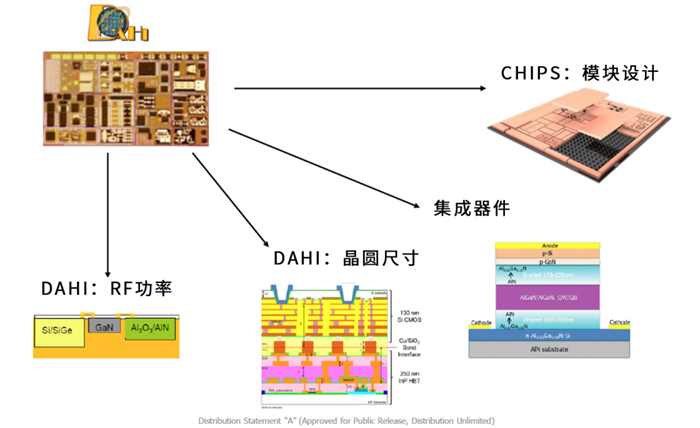

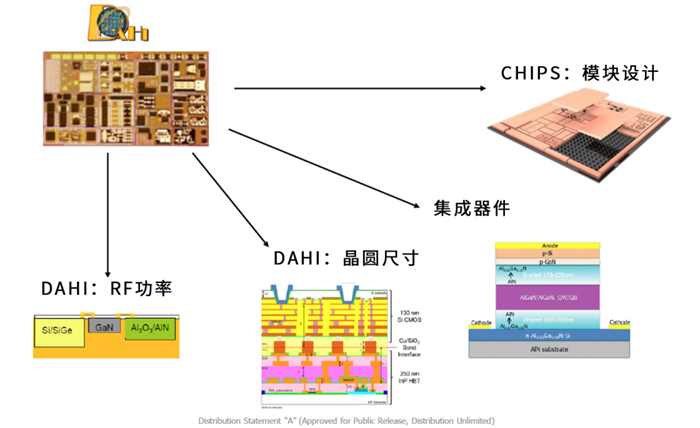

图1. 由AI、VR及AR支持的6个应用领域(来源:ASE)

Horner:这几乎与封装走线中最先进的技术一样。封装载板上走线的线宽线距曾经是10微米,而如今的尖端技术能达到8微米。芯片的尺寸已经小于1微米。芯片中介层现在已经上市,而且走线的线宽线距已经小于1微米。这类产品更倾向于采用旧技术使用的硅材料。晶片间连接的宽度和间距越窄,走线的线宽线距就越优。而且这样对于很多走线连接是最优方式,如达到每秒2千兆比特至4千兆比特的频率。

可一旦选择使用更高的数据传输率,就无法再继续使用硅中介层了。所以人们更倾向于使用有机材料,因为其损耗更低,但采用的线宽线距会变大。于是人们从芯片和封装两方面同时入手,试图解决晶片间的连接问题。

表1. 基板互连尺寸路线图(微米)(来源:HIR,2019)

Horner:我之前介绍过RDL层,大约是2微米。封装基板材料也被视为有机材料,但和有机中介层的有机成分不同,后者更多是指用于晶片间连接的RDL层。

Johnson:我们现在讨论的是含有多个芯片的半导体封装,这些芯片的功能各不相同,再加上使用不同中介层的互连结构。中介层设计必然是位于封装中间的PCB。中介层是一种IC设计,还是一种进入芯片内的PCB设计?

Horner:中介层会使用不同材料。目前最常用的是硅中介层。之前还提到过玻璃中介层。过去,封装的复杂程度远远不及今天的多芯片集成结构。所以封装基板设计使用的大量工具都无法满足复杂多芯片设计所需的带宽和功能要求。使用专为复杂SoC设计而优化的EDA工具更适合满足硅中介层的设计需求。有些供应商试图从封装角度来解决这个问题,但却收到了很多来自客户和合作方的抱怨:“器件没法用,根本不具备相应的带宽。”

要如何针对信号完整性分析建模呢?又如何为电源完整性分析建模?如何从不同技术方面综合信息?即使是芯片EDA工具都无法做到这一点,因为在通常情况下,设计一个IC时只需一次处理一种技术,也就是14纳米技术。需要大幅改善工具环境才能集成多项技术,才能进行建模、分析,在多晶片环境下进行验证。

Johnson:这就给IC设计团队增加了需要具备不同知识领域的要求。

Horner:所以我刚才提到需要创建合作环境。这不仅仅是IC设计的问题,也不仅仅是封装设计人员的问题或信号完整性问题。所有相关方都应该共同合作,以最优方式解决这一问题。

Johnson:此时,是否意味着PCB设计经验对于IC团队而言非常宝贵?你是否希望聘用具备电路板从业经验的人来处理芯片内的互连结构?

Horner:想要更高效地设计,则不应该把PCB设计当成事后需要考虑的内容。现在考虑的是将封装尺寸变成100毫米×100毫米,这个尺寸本身就几乎是一块PCB的大小了。上面会有很多小球用于连接,意味着会有很多层,导致终端产品非常昂贵。可以通过合作的方式创建一个更优的环境,从而优化每一个设计层。

标签:

#认证与标准

#路线图

#IEEE

#企业管理与运营

#Synopsys

#IC

#PCB

#封装

#异构集成