电源分配网络中的敌与友

对于高速信号完整性,高频损耗通常被是想要最大程度消除的不良副作用。另一方面,DC损耗不太重要,因为在很多高速信号方案中会有意屏蔽信号的DC分量。

本篇专栏文章的题目还可以写成“损耗可能有正面影响,而电感可能会带来负面影响”。现在这个标题显然是为了吸引眼球,我们总能找到信号完整性中出现的反例,也就是说最小化损耗的方式可能会适得其反,或至少会产生负面影响。而在电源完整性领域则恰恰相反:为了传递DC电源,我们要最大程度地减少DC损耗,与此同时又不想让高频噪声沿着电源分布网络传播。因此,电源分布中的AC损耗通常是有益的。

但电感则不同;电感存在于电流流经的所有导电结构,在电源完整性领域,只有在低通滤波过程中为了隔绝噪声故意(或偶然)在串联路径上引入的电感才是有益的电感。有些应用中我们并不需要阻止或者不在乎电源噪声沿着PDN结构传播,电感增加带来的负面影响就需要更多电容来平衡。本篇短文会展示一些仿真结果来阐释这些要点。

简化后的框图(图1)展示了并联PDN和PDN滤波器之间的差异,在并联PDN中我们并未有意在电源分布网络中放置串联元件,而在PDN滤波器中则有意(或考虑)放置串联元件来实现滤波。这张框图经过高度简化:并联PDN路径中有3个电容器,但可以是混合使用相同值和/或不同值的电容器。

.jpg)

图1:PDN系统框图表明了并联PDN和PDN过滤器的定义

PDN滤波器与之类似,但要更复杂一些,在其有完整的并联PDN,由多个电容器组成。串联电路也可更复杂一些,比如在导电元件周围放置串联和并联电阻。图2展示了负载点、端到端电源分布网络的简化示意图,其中明确指出了串联阻抗和感抗。

.jpg)

图2:简单负载点PDN的LTSPICE原理图

我们可以假设图2中所有感抗都属于副作用,也就是层、导线、走线、连接器和电容器的寄生效应。在LTSPICE中,电感器和电容器可能会从部件产生寄生效应,如此一来就不需要单独采用电路元件来模拟寄生效应,相应地就能加快仿真速度。串联和并联电路上的多处感抗,再结合容抗,就会产生大量可能会引起问题的谐振。我们在之前的专栏文章中专门介绍过此类电路的模拟和分析[1]。

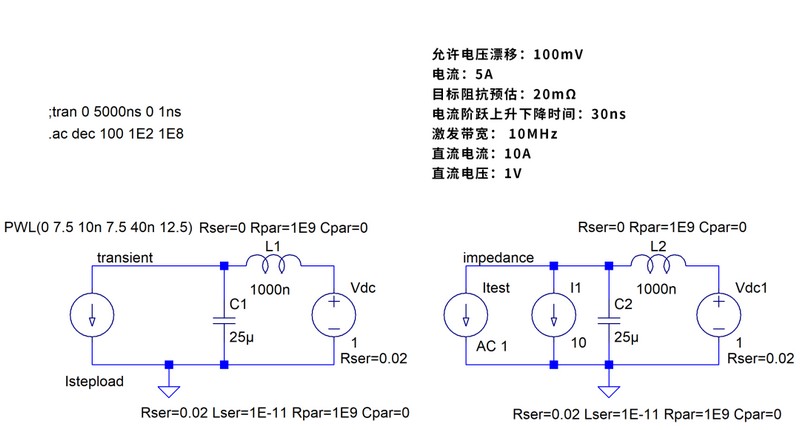

为了展示电源分布路径中未预料到或偶然出现的串联感抗所带来的后果,我们可以使用L-C电路将PDN电路简化成电源和耗电器件之间的单段接口。图3展示的电路采用了指定的元件值。左侧电流源表示耗功率器件(负载),整个电源分布网络都简化成了一个集总L-C电路。从允许范围内的电压波动到假定的瞬变电流,我们得出的目标阻抗是20 mΩ。相应地,源端阻抗也设定为20 mΩ,在PDN中选取的L和C组成的平方根(L/C)等于源端阻抗,就好比我们在信号完整性中使用的单段传输线模型。这三个数值保持一致,才能保证阻抗曲线呈平滑的形态且瞬态响应单调。

.jpg)

图3:匹配了相应源端和负载端的一级L-C PDN电路的LTSPICE原理图

我们为什么要为此图选择1 nH这个数值?仅仅是因为单个导通孔中得到的电感数值可能为1 nH,但如果我们假设使用的是10A DC电流,那就不宜直接通过单个导通孔。在真正的系统中,1nH串联感抗可能会代表整个PCB结构的感抗。图4是从负载端看模拟阻抗和瞬态响应到负载电流阶跃的瞬态响应。我们看到,若想得到2.5 F容抗的明显响应,只需要在20 mΩ阻抗下平衡1 nH的感抗。

.jpg)

.jpg)

图4:图3所示电路的阻抗曲线(左)和瞬态响应(右)

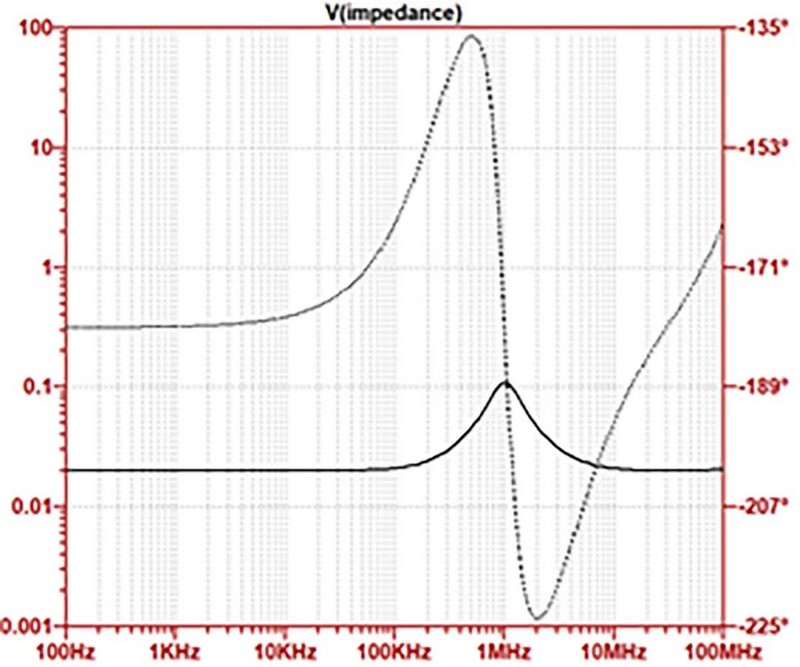

我们可以将图3和4中的案例作为基准线,探究串联感抗因某种原因升高之后会发生什么。例如,我们可以把感抗升高到10nH,其他条件(包括寄生效应)保持不变。结果如图5所示。频率响应中,1 MHz频率时达到峰值,当阻抗升高到100 mΩ时,瞬态响应中得到 MHz的振铃。在实际系统中,10 nH的感抗可能来自连接器或较短的导线,或等效于大带宽稳压器的输出感抗。为了补偿升高的感抗,唯一的选择就是按比例增加容抗。如果我们用10 nH感抗和25F容抗模拟图3中的电路(其他条件保持不变),得到的响应和图中的完全一样(图4)。

.jpg)

图5:将图2中电路串联感抗从1 nH升高到10 nH

得到的阻抗曲线(左)和瞬态响应(右)

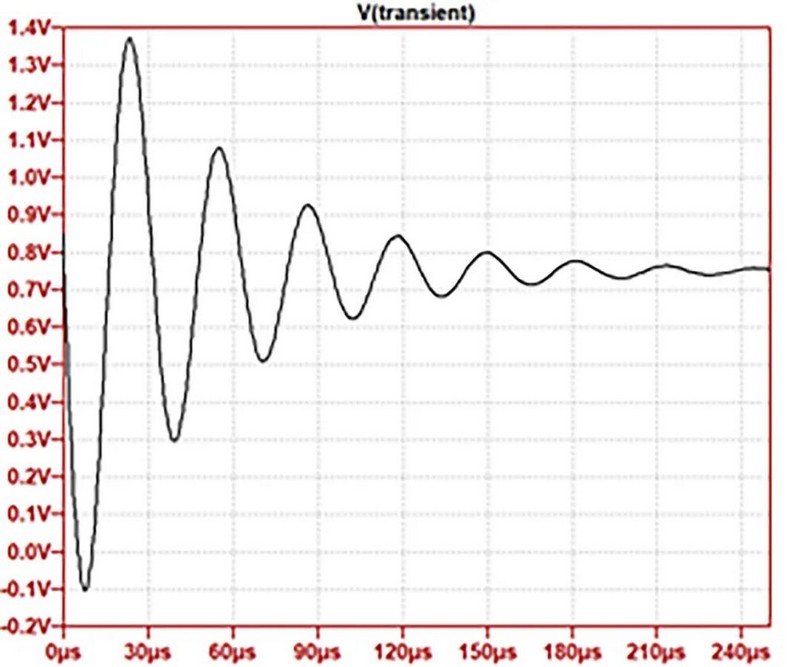

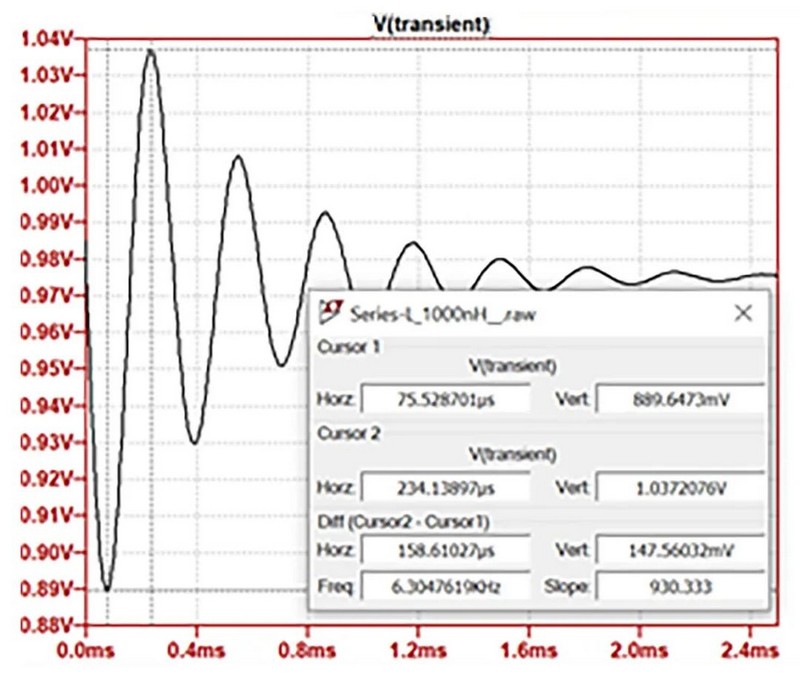

我们将重新平衡后且带有10nH感抗和25F容抗的电路当做新的基准线,看电感进一步从10 nH 升高到1000 nH或1H后会发生什么。1H感抗表示用1m长的导线对把电路连接到电源上。我们更改了多项数值,所以得到图6中的图形变化并在图7中显示结果。注意瞬态响应中水平刻度上的膨胀:阻抗曲线中30 kHz的峰值产生了巨大的振铃。如果是在实际电路中,电压会在短时间内出现负向摆动。

图6:图3的电路有1000 nH感抗和25 F容抗

我们已经知道这个问题的解决办法:若想在20 mΩ阻抗下平衡1H感抗,需要2500F的容抗。在实际系统中,用长导线连接或低带宽有源电源产生1H感抗,实际需要2500F之多的容抗来降低低频峰值。如果这样做,瞬态响应又会恢复到我们在图4中看到的那样。

图7:图6电路中的阻抗曲线(左)和瞬态响应(右)

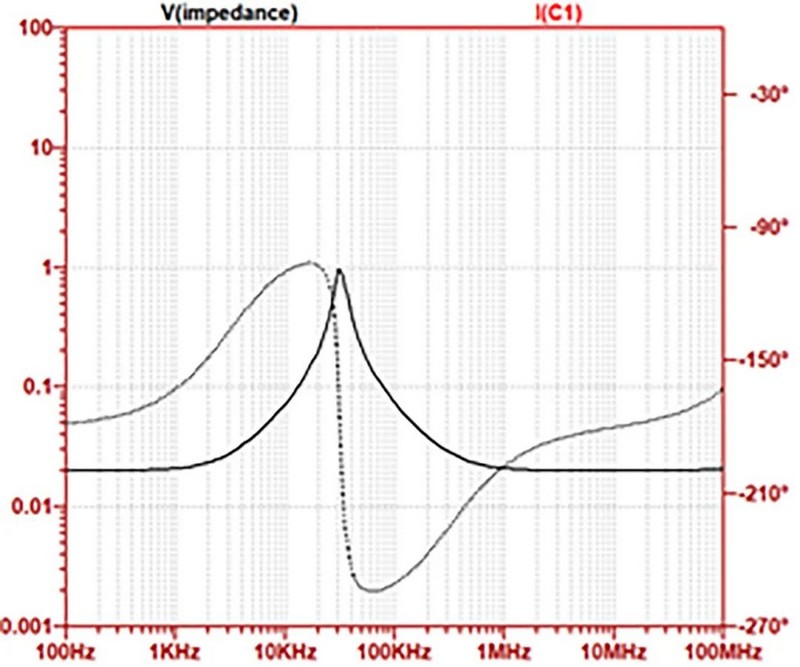

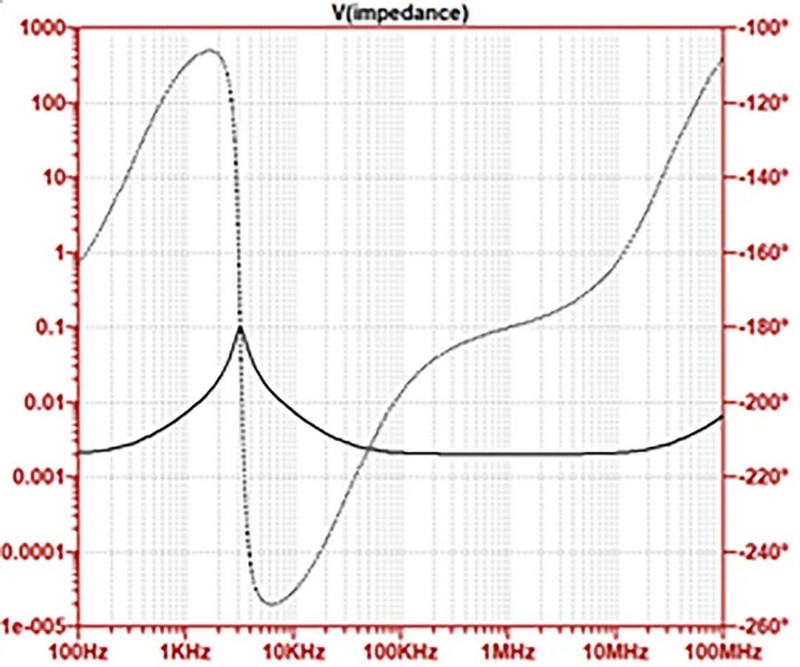

最后,为了进一步阐述电源分布系统中AC损耗的益处,我们用图8和图9展示了如果使用最新设计并只降低“损耗”后的效果,从20 mΩ到2mΩ的电源阻抗和有效的电容串联阻抗都包含在内。

.jpg)

图8:AC损耗产生的影响

图9:将AC损耗降低10倍之后的阻抗曲线(左)和瞬态响应(右)

150 mV的恒定压降和100 mV的瞬态压降可以按照20 mΩ源端阻抗和7.5A 及12.5A电流计算,现在得到的DC漂移要小10倍,振铃达到150 mVpp左右。表面看起来似乎是有所改进,但我们要记住,在最坏情况下瞬态噪声可能会大很多。当电流瞬态反复达到3.15 kHz谐振的时候就会出现最坏的情况:在第十个周期后,正弦振铃的值达到638 mVpp,是100 mΩ阻抗峰值乘以5 App瞬态电流的4/PI倍。4/PI倍表示傅里叶变换中方波基频幅度的大小 。

总结

电子线路中的感抗是不可避免的。为了最大程度减少电源轨道上的电压波动,我们需要用足够的容抗来平衡感抗。我们需要的平衡容抗与感抗呈线性正比,且随要实现的阻抗的平方倒数而变化。

作者:Istvan Novak

Istvan Novak任Samtec公司信号和电源完整性首席工程师,在高速数字、RF、模拟电路和系统设计领域有30多年的从业经验。他出版过两本关于电源完整性的书籍,同时也是信号和电源完整性课程的导师,并创建了有关SI和PI技术的网站。

欢迎扫码关注我们的微信公众号

“PCB007中文线上杂志”

点击这里即可获取完整杂志内容。

.jpg)