线上研讨会

当我们在考虑降低印刷电路板(PCBs)成本的时候,似乎第一选择是要求制造商提交更低的报价。这种做法既不健康也不合理。因为供应商是你的技术合作伙伴,你需要他们在财务上保持健康。

相反,如果我们了解PCB材料也是成本节省的新的领域,我们就会发现一片节省成本的沃土,而且这片沃土是OEM公司能够掌控的。

许多OEM公司认为拼板只是一项制造任务,并盲目地将PCB拼板任务委托给他们的供应商来做。其实,这样的做法会让OEM公司错失节省PCB材料成本的机会,因为PCB材料是PCB的主要成本影响因素之一。

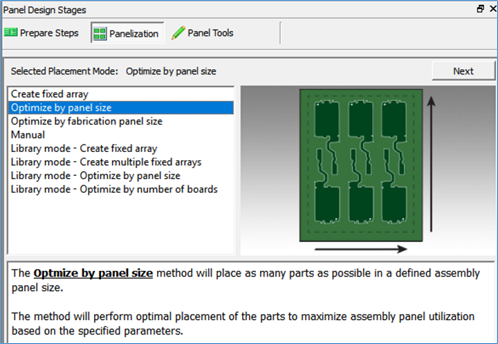

通过此次研讨会,我们将展示客户如何利用西门子EDA的Valor NPI智能化的拼板工具,让OEM公司能够在研发的早期就开始介入拼板的设计与优化,同时能综合考虑最优的拼板利用率,实现最具成本优势的PCB拼板设计。

本次研讨会,您将了解

- 如何优化您的SMT拼板与板厂拼板

- 如何利用Valor NPI的拼板工具管理拼板要求,减少逆向工程带来的风险。

- 如何在研发早期考虑拼板成本

- 如何通过Valor NPI提升您的拼板利用率

降低成本和提高效率的机会

在样机阶段,研发常常会忽视PCB材料成本的重要性,因为样机的数量通常很少。影响样机PCB成本的主要因素是PCB的交付时间、PCB是否有特殊加工要求、PCB的材料类型和PCB的表面工艺等。通常情况下,一旦样机调试通过后,用于样机生产的PCB拼板方案将被当成可行的拼板方案。然而,可用的拼板方案和经过优化的拼板方案是两个概念。

此外,在“设计到制造”的设计发布流程中,拼板的设计效率是非常低下的。典型的流程是PCB研发人员先按照SMT工艺提供的拼板要求来绘制他们的SMT拼板图纸。然后,研发将SMT拼板图纸发送给PCB供应商,PCB供应商需要重新理解拼板图纸,并在其CAM软件(PCB供应商拼板设计软件)中重新输入SMT拼板配置,生成一个新的拼板图纸,将其发送回研发进行确认,确认通过后再进行生产。只有这个时候,研发才知道每次试产需要加工的拼板数量,以及PCB的报价。在整个“设计到制造”的流程中,浪费了太多的人力和资源,这样的流程其实可以变得更简单。

更好的流程是,研发人员应该综合考虑SMT的拼板要求和PCB供应商的拼板要求,将这些要求整合到拼板工具中,并且这一工具输出的拼板方案可以直接被PCB供应商识别并使用,这样才可以消除多次解读拼板图纸带来的风险,以及重复创建拼板图纸造成的时间浪费。另外一个真正的好处是,研发还可以尽早对拼板材料成本进行了解。这有助于通过优化拼板来降低PCB材料成本。

有了对拼板成本的预见性,研发人员甚至可以评估修改PCB外形,进一步提高PCB的材料利用率,从而达到节省成本的目的。例如,某手机研发公司的PCB研发人员通过重新定义SMT拼板的布局,利用互相嵌套的拼板布局(重新定义拼板布局不需要花费任何费用)来设计SMT拼板,他们成功将PCB材料利用率从52%提升到88%。

拼板工具中的几种快捷拼板模式

预防问题,而不是等到最后来解决问题

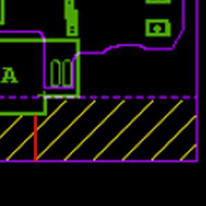

另一个重要的考虑是,如何保证拼板不引入制造问题?拼板中的许多制造问题的产生,其实都是设计过程中无意引入的,而这些问题通常只有等到PCB供应商来告诉你。更糟糕的是,其中一些问题可能直到生产线生产过程中才会显现出来,这将是一个代价昂贵的错误。因此,需要拼板工具在设计拼板的过程中,同时检查拼板的可制造性问题,避免这些问题的发生。

Valor NPI是行业内最领先的DFM检查工具,包含上千条DFM检查项,并覆盖所有产品类型,包含刚性板、柔性板、刚柔结合板、HDI板甚至封装基板,对于拼板检查方面,Valor NPI也集成了丰富的检查规则,完全可以让你在设计的过程中就预防可能出现的拼板DFM问题。

元件距离拼板边缘太近,有损坏的风险

元件距离拼板边缘太近,有损坏的风险

节省板材的案例

让我们再来谈谈板材利用率。PCB供应商提供的板材利用率通常令人印象深刻,比如超过60%,听起来很高,但实际上是不切实际的。制造商所说的板材利用率是SMT拼板总面积占PCB板厂拼板总面积的比值。SMT拼板和PCB制造拼板多数情况都是矩形,矩形之间的匹配性非常好,所以你可以看到一个很高的板材利用率。

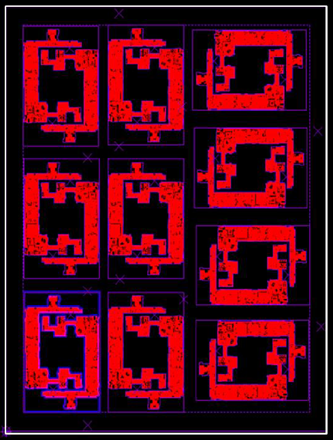

实际上,研发真正应该关心的是单板的总面积与PCB板厂拼板面积的比值,而不是SMT拼板与PCB板厂拼板的比值,因为单板才是最终实际有效的产品。如下图所示,PCB供应商报告的板材利用率为58.9%,但由于PCB板的特殊形状,实际单板的板材利用率仅为18.7%。

PCB板厂提供的板材利用率是58.9%,而以单板为基准计算的话,实际上只有18.7%

PCB板厂提供的板材利用率是58.9%,而以单板为基准计算的话,实际上只有18.7%

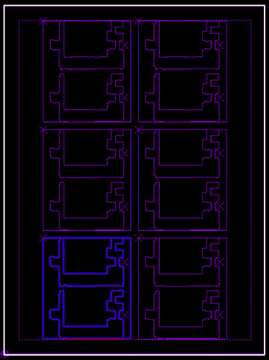

印制板1是一款刚性印制板。从下图可以看出,在拼板优化之前,使用18x24英寸的PCB板材的情况下,这款PCB的板材利用率是18.7%,每个PCB板厂拼板由6个2拼的SMT拼板组成。当采用西门子EDA EDA公司的Valor NPI专用拼板软件优化之后,这款PCB可以达到31.5%的板材利用率,每个PCB板厂拼板可以包含10个2拼的SMT拼板。Valor NPI拼板设计和优化模块可以自动的将单板嵌套成更紧密的SMT拼板,从而提高PCB板材利用率。

SMT拼板和PCB板厂拼板同时优化后的拼板布局

对于这个案例,我们假设订单数量在100到2000之间,以100递增(下图横向坐标值*10为订单数量), 然后计算拼板在优化前后的成本变化。

对于所有的数量组中,优化后的拼板都显示了显著的成本节约

总结

OEM公司是产品成本的最直接管理者和收益者,包括PCB成本。虽然供应商也会对拼板做一些优化,但OEM公司如果不主动在设计阶段对拼板进行自主设计与规划,很难控制PCB的拼板成本。采用西门子EDA EDA公司的Valor NPI拼板工具,OEM就可以在拼板设计和优化中采取主动, 并可以获得显著的PCB材料成本节约,加快产品推向市场的时间。

记住,你可能认为你只支付了单板的费用,其实你付的是拼板的钱。你购买的越多,你的成本越高。

本次研讨会,我们将介绍如何使用Valor NPI在几分钟内来创建和优化拼板,同时会兼顾拼板的质量和成本最优化,通过Valor NPI完成的拼板数据,还可以直接用于PCB板厂生产,可以节省与PCB制造商大量的反复沟通时间。

研讨会主题

如何通过拼板设计降低PCB成本

时间

2021年9月8日 20:00

主讲人

季伸彪

季伸彪在西门子EDA担任技术市场工程师,2019年加入西门子EDA,此前曾经在国内大型EMS公司及国内知名通讯公司任职,深刻了解DFM在PCB设计与制造中的优势,2006年开始从事DFM相关岗位,2011年开始从事Valor NPI技术相关岗位。

报名方式

报名方式

扫码报名

来源:Mentor PCB及IC封装设计