第4篇“技术讲座”专栏文章主题是SAP技术,介绍IC异构集成策略。在2000~2010年之间,Karl Dietz也在其“技术讲座”专栏文章中多次介绍了适用于IC互连的高阶PCB技术[1-2]。

简介

IC功能的进一步扩展通常伴随着IC结构的缩小,这一概念由Gordon Moore首先提出,从那以后就被称为“摩尔定律”。但现在IC结构已经缩小到5nm以下,制造这种结构所需的成本和难度已经阻碍了进一步扩展IC的功能。解决方案似乎是将IC晶片组合在同一块基板上形成系统级封装(system-in-package,简称SiP),这种结构也称之为异构集成(heterogeneous integration,简称HI)。

异构集成

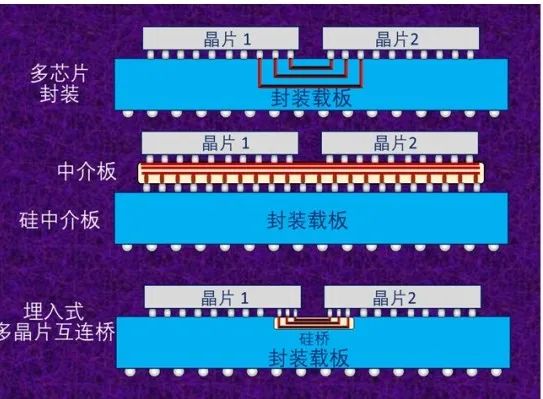

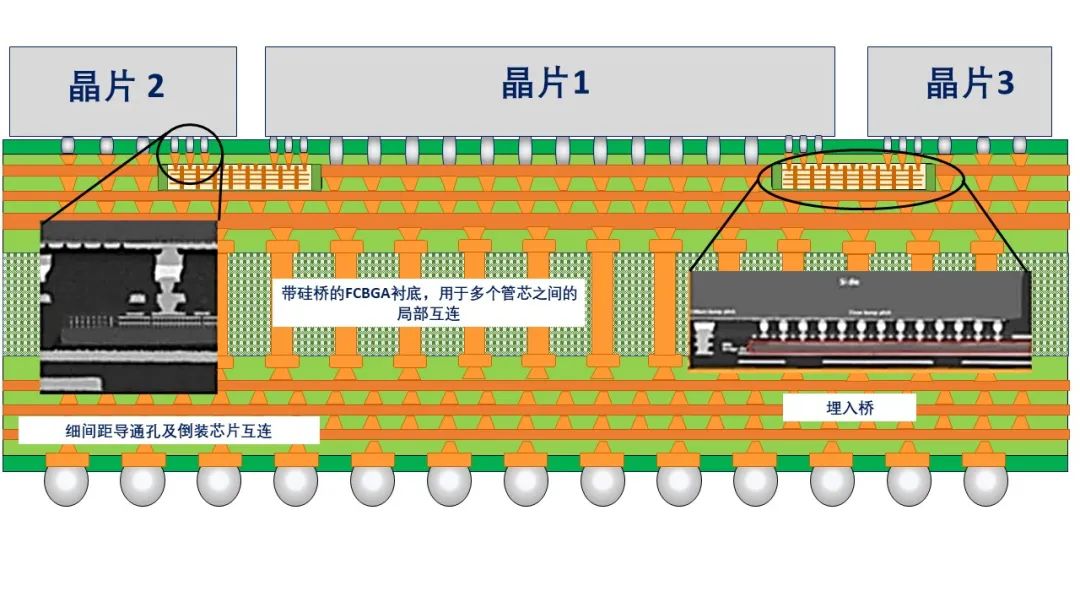

半导体晶体管的体积不断缩小,于是人们也发现了成本更低的方式——将体积较大且结构复杂的晶片分解成体积较小的晶片,然后采用极其精细的线宽和线距及尺寸非常小的通孔将小晶片、模块化晶片(现称为小chiplet)、小分离元件放置在同一块有机载板上。通常有3种实现这种目标的架构(图1):

-

在使用了PCB、玻纤或陶瓷材料的封装载板上放置多个IC晶片

-

晶片和封装之间有硅或玻璃中介板

-

封装载板中使用小型内嵌硅桥连接各个晶片和分离元件

图1:异构集成封装方案更倾向于使用这3种架构[3]

(来源:ASM NEXX)

多芯片封装

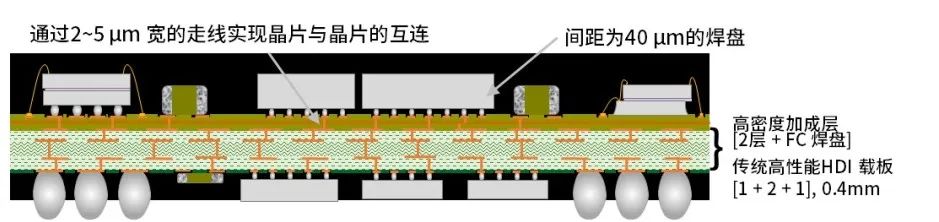

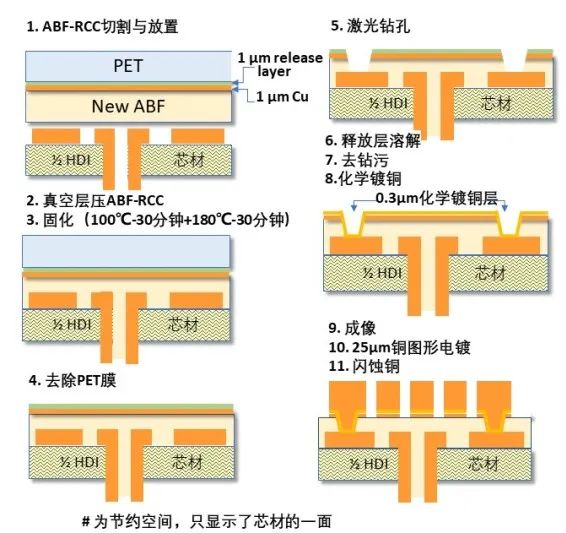

目前所使用的传统倒装芯片是球栅阵列封装(图2)。这种结构是在传统高性能HDI基材(1+2+1)上添加1~2层ABF膜(Ajinomoto build-up film,简称ABF)。新的ABF工艺使用耐高温RCC(通常为聚亚酰胺)材料,可承受温度更高的组装工艺(见图3)[4]。

图2:双面模塑球栅阵列使用了ABF和高性能HDI[4]

(来源:《半导体工程》)

图3:使用了ABF加RCC的新制造工艺[5]

(来源:《ABF技术报告》)

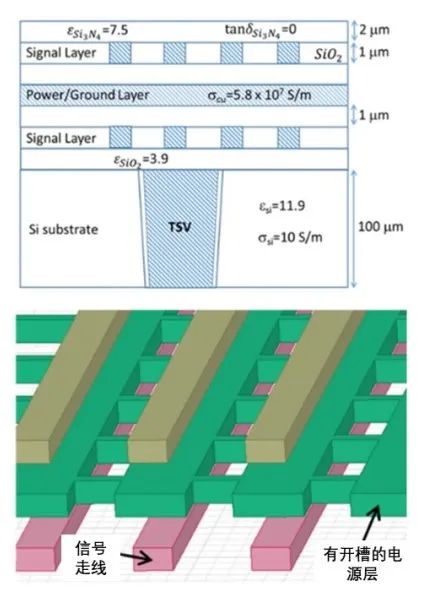

硅中介板

HI的复杂程度日益增加将为载板增加更多功能,形成如图4所示的模块,其中包含各种材料/连接方式的IC芯片、埋入元件、RF/天线、光波导甚至能量存储。

图4:硅中介板具备CTE及密度优势,但对于TSV而言成本会增加[6]

(来源:《HIR发展路线图》)

埋入式多晶片互连桥

Intel公司提议在载板中使用埋入式多芯片互连硅桥接(embedded multi-die interconnect bridge,简称EMIB),可以在实现所需中介板互连密度的同时降低封装载板的成本(图5),于是第三种结构应运而生。

图5:EMIB能使传统多芯片封装载板达到高成本硅中介板所能达到的晶片间密度[7]

(来源:《HIR发展路线图(2020版)》第10页, Intel)

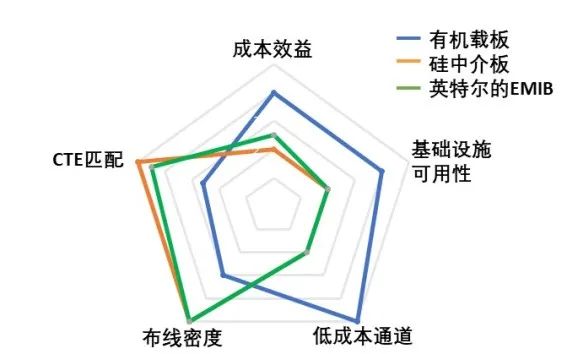

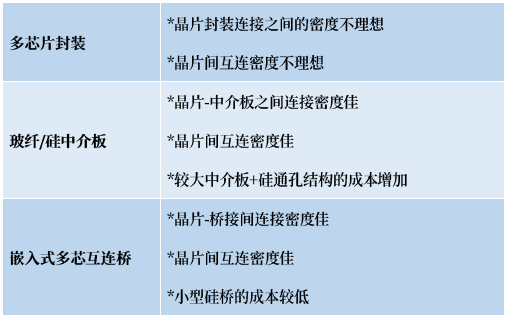

表1和图6比较了这3种HI封装的优缺点。

图6:3种HI封装结构的5大特点[6]

(来源:《HIR发展路线图》)

表1:3种HI封装的优缺点对比[6]

(来源:《HIR发展路线图》)

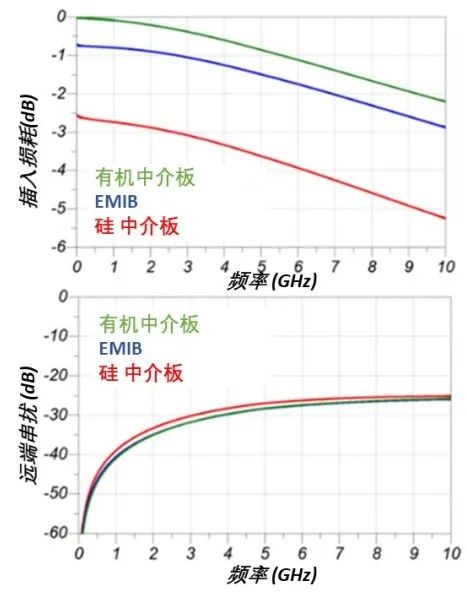

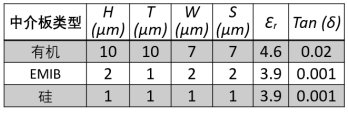

表2和图7对比了材料的频率性能。LCD中显示器使用玻纤作为硅的主要替代材料。

图7:3种封装的频率性能[6]

(来源:《HIR发展路线图》)

表2:封装载板替代材料的结构和特点[6]

(来源:《HIR发展路线图》)

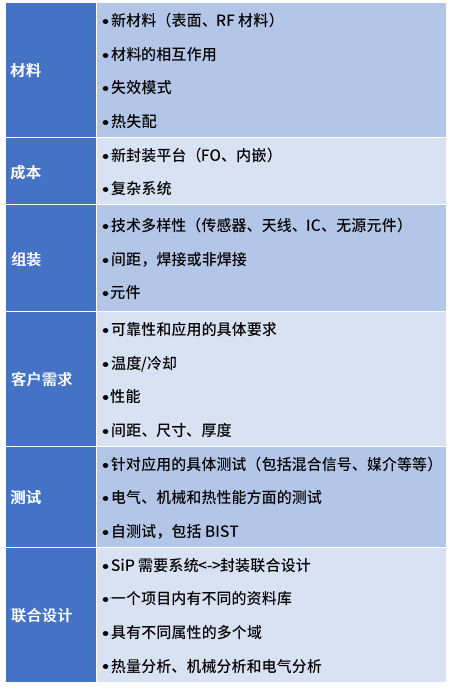

PCB制造厂实施IC封装新技术面临的挑战

全球大约有6~8家有机IC载板制造商,并且全都位于亚洲(日本、中国台湾地区、韩国和马来西亚)。目前中国大陆还没有这样的制造商,但这种局面不久之后应该会被打破。所有这些制造商都会转向HI载板批量生产。如果北美和欧洲地区的制造商计划生产新型HI载板,需要应对以下挑战。

-

材料:ABF或类似薄膜需要使用专用的真空层压设备,同时还需要掌握加成法工艺中铜的表面制备技术。

-

成本:需要最小化或避免使用人工密集型后端工艺流程(这样会导致其他北美地区的IC载板制造厂倒闭)。

-

组装:目前北美地区没有OSAT半导体批量组装厂;需要构建这样的组装厂。

-

客户支持:需要增加客户咨询、建模和工程设计接口。

-

测试:测试HI载板的技术变得更加专业化,且要制造出所需的治具。

-

联合设计:必须确定HI载板制造商是否需要具备类似于当今IC封装和OSAT供应商的EDA设计和建模能力。

表3列出了所有需要应对的挑战。

表3:实施新技术面临的挑战

总结

针对新型异构集成系统封装方案所进行的探索才刚刚起步。这项技术的基础是目前正在使用的FCBGA、硅中介板和2.5D封装方案,但更侧重于降低成本、提高性能以及可用性。图8所示是Intel的EMIB和Foveros技术理念,这种技术可为新一代产品提供高密度解决方案。

据预测,未来5年PCB制造业中增长最快的产品是高密度HDI(6.8%)和芯片载板(9.7%),具体详情见《IPC-北美地区高阶封装生态系统差距评估报告》的表4所示。可在IPC网站免费下载该报告[8]。

欢迎扫码关注我们的微信公众号

“PCB007中文线上杂志”

点击这里即可获取完整杂志内容。