多年来,Z-zero公司创始人Bill Hargin一直在研究叠层设计技术。他开发了PCB叠层规划软件,并撰写了《印制电路设计师指南——叠层设计:设计中的设计》一书。

此次采访中,Bill分享了他对设计刚挠结合叠层的观点,该技术带来的挑战,以及刚性板设计师如何在3D中设计叠层的关键。Flexible Circuit Technologies公司的Mark Finstad和TTM Technologies公司的Nick Koop,这两位挠性专家也对刚挠结合设计师面临的许多权衡提出了建议。

Andy Shaughnessy:你撰写了关于叠层设计方法的专业书籍,其中设计师在设计刚挠结合叠层时面临哪些特有挑战?

Bill Hargin:正如我经常说的,机械世界和电气世界是相互冲突的。如果不涉及物理/机械世界,我们就不需要担忧信号完整性。

刚挠结合结构具有许多优点——可靠性、动态弯曲以及能够在狭小空间内完成任务。但是,需要管理具有额外维度或“自由度”的机械世界会带来额外的负担。例如,可以很容易地在2D中查看刚性叠层,而对于大多数电气硬件工程师来说,刚性叠层领域相对容易理解和管理。只需关注阻抗、频率和损耗,以及驱动它们的物理和电气参数。当挠性分叠层出现在画面中时,挠性部分需要弯曲的事实将其变成需要时间学习的3D机械工程设计问题。这是真正需要依靠挠性制造商专业知识的地方。为此,我决定拜访“挠性专家”,包括Flexible Circuit Technologies公司的Mark Finstad和TTM的Nick Koop。以下内容既有他们的想法,也有我自己的一些想法。

图1:典型的刚挠结合板

Mark强调,刚挠结合叠层必须将刚性和挠性基材混合到终端产品中,并且由于蚀刻和层压等工艺,这些材料均以不同的速率拉伸和收缩。此外,挠性材料可能会因为温度和湿度的变化而拉伸和收缩。更为复杂的是,这些材料在X轴和Y轴上的移动速度通常不相同。大多数制造商在许多材料方面都有着丰富的经验,他们了解如何通过缩放底片和应用程序来解决尺寸不稳定性问题。此外,激光直接成像、智能激光,以及机械钻孔有助于解决许多问题,但使用这些加工工具确实需要支出一定的成本。

Shaughnessy:关于刚挠结合设计和叠层,刚性板PCB设计师需要了解什么?

Hargin:我不知道刚挠结合设计及叠层否会流行起来,但我已经开始把刚挠结合设计称为“在3D中设计”或“3D设计。

近年来,刚挠结合PCB与HDI的市场呈上升趋势。年轻的工程师最好开始将刚挠结合设计技能添加到自己的技能库中,以增加职业机会。也许可以从我关于叠层的书中刚挠结合章节开始着手了解相关知识。为了信号完整性和EMI控制,我们希望电流返回路径具有邻近的参考平面。但额外的平面层会减小弯曲半径,因此在设计挠性时需要进行许多新的权衡。

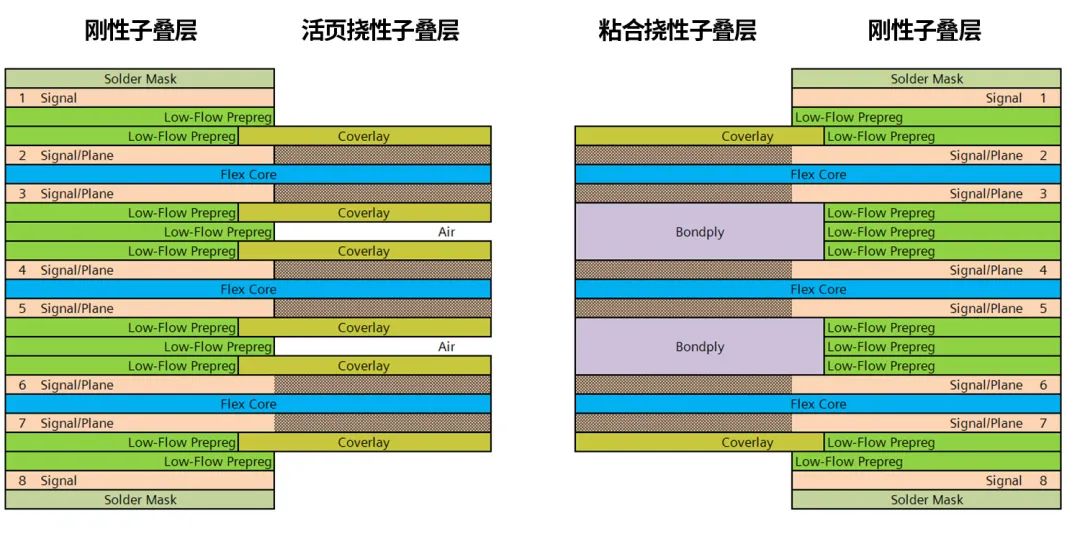

在设计刚挠结合项目时,应该考虑与刚性PCB相关的一些重要差异。可以使用活页或粘合方法连接挠性芯材(图1)。

图2:活页设计在90︒和180︒弯曲时最灵活。它们的制造最简单,但不建议用于阻抗控制。粘合的挠性较低,因此需要更大的弯曲半径

采用活页设计,单个挠性芯材之间有气隙,从而可获得成本更低、更灵活的设计。粘合设计需要使用粘合层和半固化片进行额外的层压处理,从而导致更刚性的设计。尽管比活页设计至少厚20倍,因为可以严格控制电流返回路径,改善了带状线阻抗控制。

Nick提到,阻抗要求可能会导致介质变厚,同时较厚的材料会导致弯曲性降低。此外,虽然可以在挠性层上蚀刻任何线宽,但更宽的走线在机械上能够承受更多的弯曲和挠折。

Mark补充道,如果设计刚挠结合电路时只考虑到电气要求,那么最终可能会得到电气完美的刚挠结合电路,但当弯曲它时,其走线会开裂。因此,如果电路不能形成最终结构且不会造成损坏,那么所有极佳的电气特性都是毫无意义的。

从成本的角度来看,Nick提出设计师应该意识到刚挠结合电路板的制造方式。例如,通常并非所有层都需要出现在所有刚性部分。然而,从刚性部分而不是其他部分去除铜层和相关介质,将会增加制造成本。使所有刚性部分具有相同的材料叠层,成本会更低。可以蚀刻去除不需要的铜,但可保留所有的介质。

Shaughnessy:材料选择如何影响刚挠结合电路的叠层规划?

Hargin:在选择材料之前,需要了解有哪些选择。刚性PCB有芯材、半固化片和用于介质的阻焊膜。在刚挠结合世界中,芯材被挠性芯材取代,半固化片包括“无流动”和“低流动”两种类型,还有粘合层、覆盖层和增强板。

刚挠结合设计中的铜以各种方式附着在挠性介质上。可以在铜直接粘合到基材上的地方添加粘合剂。有时会添加增强板来加固用于元器件放置或布线孔的挠折区域。铜可以电沉积(ED,挠性较低,成本较低)或轧制退火(RA,挠性较高,成本较高)。挠性平面通常蚀刻有网格图形,因为铜的减少使其更可弯曲。

覆盖层是可弯曲材料,通常位于挠性子叠层的外部。它们保护和隔离表面的挠性电路,防止其浮起。覆盖层通常由丙烯酸、聚酰亚胺或聚酯制成。典型的覆盖层结构(图2)顶部有聚酰亚胺介质,面向铜的一侧有粘合剂。

3:两个导电层之间有挠性芯材,外部有粘合剂和覆盖层

粘结层类似于覆盖层,但它们用于内部带状线层,两面有粘合剂,中间为聚酰亚胺介质。如果想把两个挠性芯材粘在一起,就需要粘合层。

挠性芯材通常横跨所有子叠层,将铜从一端运送到另一端。挠性芯材的常见品牌是杜邦Pyralux或松下Felios,这两个产品系列的侧重点不同。无粘合剂的挠性芯材用于高性能的刚挠结合应用;基于粘合剂的挠性芯材成本较低,通常用于单面或双面或低层数的挠性应用。

在刚性子叠层上使用低流动及无流动半固化片代替传统的半固化片,以防止树脂流到挠性子叠层上,导致挠性区域的一部分变脆并产生可能的失效模式。无/低流动半固化片通常可用于106和1080种玻璃型号。顾名思义,低流动半固化片的流动性比无流动半固化片的流动性略高。根据我的研究,低/无流动半固化片可从AGC Nelco、Arlon、Isola、TUC、Showa Denko(前身为日立)和Ventec等供应商处获得。

低流动半固化片通常是一层叠在另一层上面,外层到达刚性边缘,而内层凹缩50密耳,以便挠性子叠层的覆盖层可以嵌入到刚性板中,并由外层低流动半固化片固定(图3)。

图3:挠性叠层的覆盖层嵌入刚性叠层的过渡区内

挠性芯材和粘合层、聚酰亚胺膜和覆盖层没有玻纤布,但如前所述,无流动的半固化片是玻纤增强的。一旦了解了基本知识,就能够与制造商进行更有意义的对话。Nick指出,成功的刚挠结合设计师需要了解叠层中存在哪些材料以及具体的位置。例如,挠性芯材在整个叠层过程中无处不在。相反,挠性粘合层和覆盖层仅位于挠性区域,并且仅延伸一小段距离进入刚性区域,从而避免任何镀通孔区域。重要的是使任何挠性粘合剂远离刚性部分中的镀通孔,因为它具有低Tg和高CTE,这意味着进入镀通孔后会产生额外的应力。

Mark Finstad补充了以下关于材料交付周期的建议:

“有常见的材料,不太常见的材料和一些完全陌生的材料可用于制造刚挠结合电路。使用常见的主流材料进行设计通常会确保这些材料要么是现货,要么可以在最短的交付周期内采购到。如果制造商必须订购需要2~3个月交付周期的陌生材料(有时比你认为的周期要长),将不得不应对额外的时间。大多数制造商喜欢在将工作投入生产之前将材料收入仓库中,因此材料交付和加工是连续的,而不是同时进行。这可能会导致对成品的漫长等待。”

Shaughnessy:为了使制造更容易,设计师可以采取什么措施来优化其刚挠结合叠层?

Hargin:《挠性电路技术》一书的作者Joe Fjelstad说:“不要为制造而设计。而要与制造一起设计。”换句话说,他告诉我们不要单干。在有意愿、有足够的时间和资金时,可以生产很多可能不应该生产的东西,或者可以用更便宜的替代品生产。经验丰富的刚挠结合PCB制造商是很好的资源,如果有足够的交付周期,甚至可以从另一个制造商那里获取第二种意见。

Mark补充道,声誉良好的制造商可从多年来数千个成功的(也许还有一些不太成功的)设计中收获经验教训。制造商除了可以指导客户做什么,同样重要的是,为了获得成功,指导客户不应该做什么。

正如我所注意到的,有一整本书都是关于这个主题的,所以在优化刚挠结合设计时的注意事项列表可能非常详尽。Mark列出了他在刚挠结合设计方面的一些注意事项:

- 尽可能使用标准材料。

- 尽可能优化线宽/线距尺寸。如果只在少数小区域需要,不要将整个电路板默认为最小特征尺寸,这将增加蚀刻量。

- 优化焊盘尺寸。增加焊盘尺寸——即使是额外的一两密耳——也可以使制造过程变得容易得多。

- 尽可能制作100µm以上的盲孔,这将为提供最可靠的电镀通孔连接。

- 使用对称的材料叠层,以最大限度地减少回流过程中的翘曲。

- 始终使每个刚性区域具有相同的结构和层数,去除单个区域甚至几个刚性区域中的层不会节省成本。相反,将会大大增加成本。

Nick提供了自己的注意事项:

- 最好的刚挠结合叠层是对称的,以最大限度地减少翘曲。

- 最成功的设计不会将挠性层作为刚性叠层中最外层(顶部或底部)。

- 刚挠结合设计需要更大的孔环,以应对材料移动的变化。

- 相比刚性PCB,不同的材料叠层会导致更多的对准错误。

Shaughnessy:非常好。你还有什么要补充的内容吗?

Hargin:邀请一位在刚挠结合PCB制造方面有经验的PCB制造专家出去吃午饭,参观他们的工厂。更好的方法是,主动发起邀请,看看他们是否回请你吃午饭。在IPC APEX EXPO上完课后,我和Nick和Mark一起尝试了一下,结果得到了一份椒盐卷饼。这似乎很合适,因为我们谈论的主题是刚挠结合。

Shaughnessy:谢谢你,Bill。

Hargin:欢迎免费下载我写的关于叠层设计的电子书;其中有整整一章是关于刚挠结合的。

欢迎免费下载Bill Hargin撰写的《印制电路设计师指南——叠层设计:设计中的设计》。